36-18 Vol. 3C

INTEL® PROCESSOR TRACE

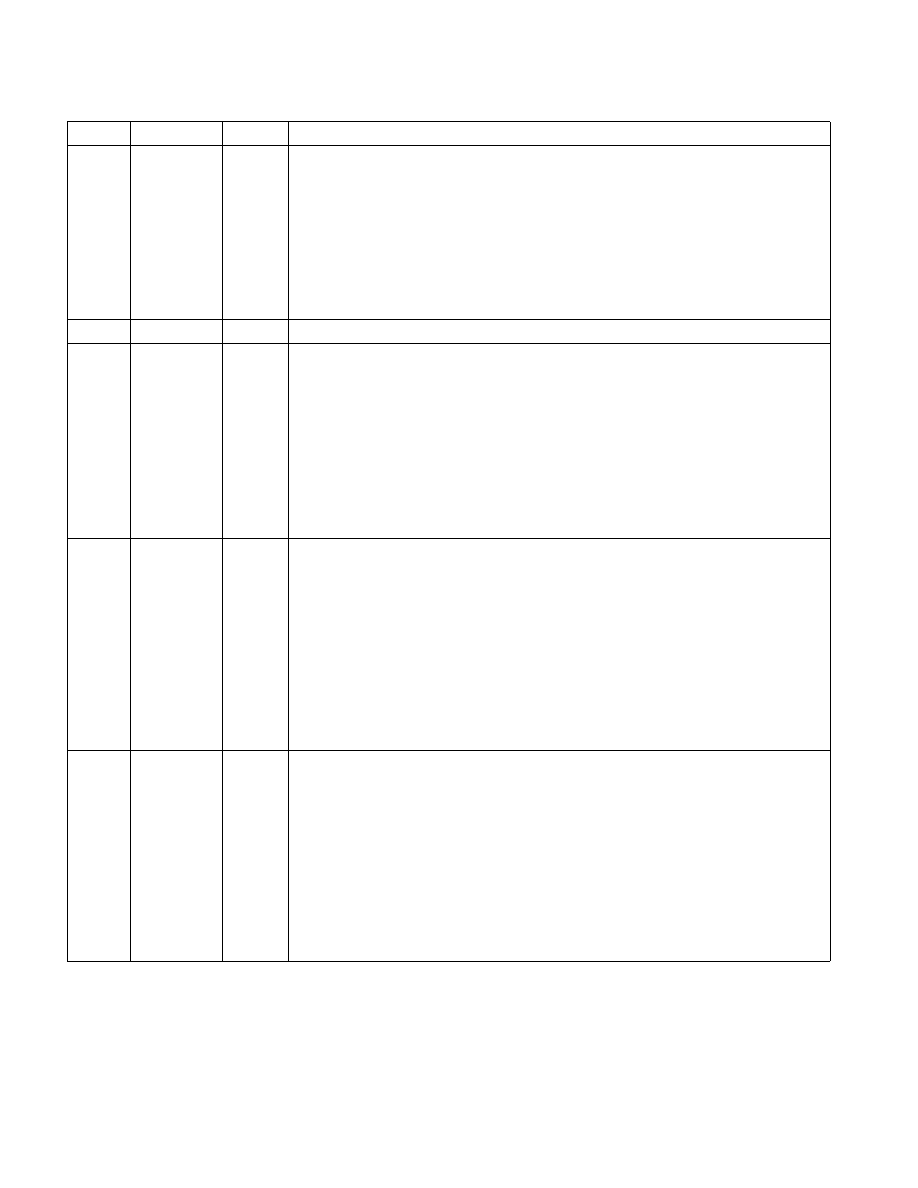

27:24

PSBFreq

0

Indicates the frequency of PSB packets. PSB packet frequency is based on the number of Intel

PT packet bytes output, so this field allows the user to determine the increment of

IA32_IA32_RTIT_STATUS.PacketByteCnt that should cause a PSB to be generated. Note that

PSB insertion is not precise, but the average output bytes per PSB should approximate the

SW selected period. The following Encodings are defined:

0: 2K, 1: 4K,

2: 8K,

3: 16K,

4: 32K,

5: 64K,

6: 128K,

7: 256K,

8: 512K, 9: 1M, 10: 2M,

11: 4M,

12: 8M,

13: 16M, 14: 32M, 15: 64M

Software must use CPUID to query the supported encodings in the processor, see Section

36.3.1. Use of unsupported encodings will result in a #GP fault. This field is reserved if

CPUID.(EAX=14H, ECX=0):EBX.CPSB_CAM[bit 1] = 0.

31:28

Reserved

0

Must be 0.

35:32

ADDR0_CFG

0

Configures the base/limit register pair IA32_RTIT_ADDR0_A/B based on the following

encodings:

0: ADDR0 range unused.

1: The [IA32_RTIT_ADDR0_A..IA32_RTIT_ADDR0_B] range defines a FilterEn range. FilterEn

will only be set when the IP is within this range, though other FilterEn ranges can additionally

be used. See Section 36.2.4.3 for details on IP filtering.

2: The [IA32_RTIT_ADDR0_A..IA32_RTIT_ADDR0_B] range defines a TraceStop range.

TraceStop will be asserted if code branches into this range. See 4.2.8 for details on TraceStop.

3..15: Reserved (#GP).

This field is reserved if CPUID.(EAX=14H, ECX=1):EBX.RANGECNT[2:0] >= 0.

39:36

ADDR1_CFG

0

Configures the base/limit register pair IA32_RTIT_ADDR1_A/B based on the following

encodings:

0: ADDR1 range unused.

1: The [IA32_RTIT_ADDR1_A..IA32_RTIT_ADDR1_B] range defines a FilterEn range. FilterEn

will only be set when the IP is within this range, though other FilterEn ranges can additionally

be used. See Section 36.2.4.3 for details on IP filtering.

2: The [IA32_RTIT_ADDR1_A..IA32_RTIT_ADDR1_B] range defines a TraceStop range.

TraceStop will be asserted if code branches into this range. See Section 36.4.2.10 for details

on TraceStop.

3..15: Reserved (#GP).

This field is reserved if CPUID.(EAX=14H, ECX=1):EBX.RANGECNT[2:0] < 2.

43:40

ADDR2_CFG

0

Configures the base/limit register pair IA32_RTIT_ADDR2_A/B based on the following

encodings:

0: ADDR2 range unused.

1: The [IA32_RTIT_ADDR2_A..IA32_RTIT_ADDR2_B] range defines a FilterEn range. FilterEn

will only be set when the IP is within this range, though other FilterEn ranges can additionally

be used. See Section 36.2.4.3 for details on IP filtering.

2: The [IA32_RTIT_ADDR2_A..IA32_RTIT_ADDR2_B] range defines a TraceStop range.

TraceStop will be asserted if code branches into this range. See Section 36.4.2.10 for details

on TraceStop.

3..15: Reserved (#GP).

This field is reserved if CPUID.(EAX=14H, ECX=1):EBX.RANGECNT[2:0] < 3.

Table 36-6. IA32_RTIT_CTL MSR (Contd.)

Position

Bit Name

At Reset

Bit Description