36-2 Vol. 3C

INTEL® PROCESSOR TRACE

— Overflow (OVF) packets: OVF packets are sent when the processor experiences an internal buffer overflow,

resulting in packets being dropped. This packet notifies the decoder of the loss and can help the decoder to

respond to this situation.

•

Packets about control flow information:

— Taken Not-Taken (TNT) packets: TNT packets track the “direction” of direct conditional branches (taken or

not taken).

— Target IP (TIP) packets: TIP packets record the target IP of indirect branches, exceptions, interrupts, and

other branches or events. These packets can contain the IP, although that IP value may be compressed by

eliminating upper bytes that match the last IP. There are various types of TIP packets; they are covered in

more detail in Section 36.4.2.2.

— Flow Update Packets (FUP): FUPs provide the source IP addresses for asynchronous events (interrupt and

exceptions), as well as other cases where the source address cannot be determined from the binary.

— MODE packets: These packets provide the decoder with important processor execution information so that

it can properly interpret the dis-assembled binary and trace log. MODE packets have a variety of formats

that indicate details such as the execution mode (16-bit, 32-bit, or 64-bit).

•

Packets inserted by software:

— PTWRITE (PTW) packets: includes the value of the operand passed to the PTWRITE instruction (see

“PTWRITE - Write Data to a Processor Trace Packet” in Intel® 64 and IA-32 Architectures Software

Developer’s Manual, Volume 2B).

•

Packets about processor power management events:

— MWAIT packets: Indicate successful completion of an MWAIT operation to a C-state deeper than C0.0.

— Power State Entry (PWRE) packets: Indicate entry to a C-state deeper than C0.0.

— Power State Exit (PWRX) packets: Indicate exit from a C-state deeper than C0.0, returning to C0.

— Execution Stopped (EXSTOP) packets: Indicate that software execution has stopped, due to events such as

P-state change, C-state change, or thermal throttling.

36.2

INTEL® PROCESSOR TRACE OPERATIONAL MODEL

This section describes the overall Intel Processor Trace mechanism and the essential concepts relevant to how it

operates.

36.2.1

Change of Flow Instruction (COFI) Tracing

A basic program block is a section of code where no jumps or branches occur. The instruction pointers (IPs) in this

block of code need not be traced, as the processor will execute them from start to end without redirecting code

flow. Instructions such as branches, and events such as exceptions or interrupts, can change the program flow.

These instructions and events that change program flow are called Change of Flow Instructions (COFI). There are

three categories of COFI:

•

Direct transfer COFI.

•

Indirect transfer COFI.

•

Far transfer COFI.

The following subsections describe the COFI events that result in trace packet generation. Table 36-1 lists branch

instruction by COFI types. For detailed description of specific instructions, see Intel® 64 and IA-32 Architectures

Software Developer’s Manual.

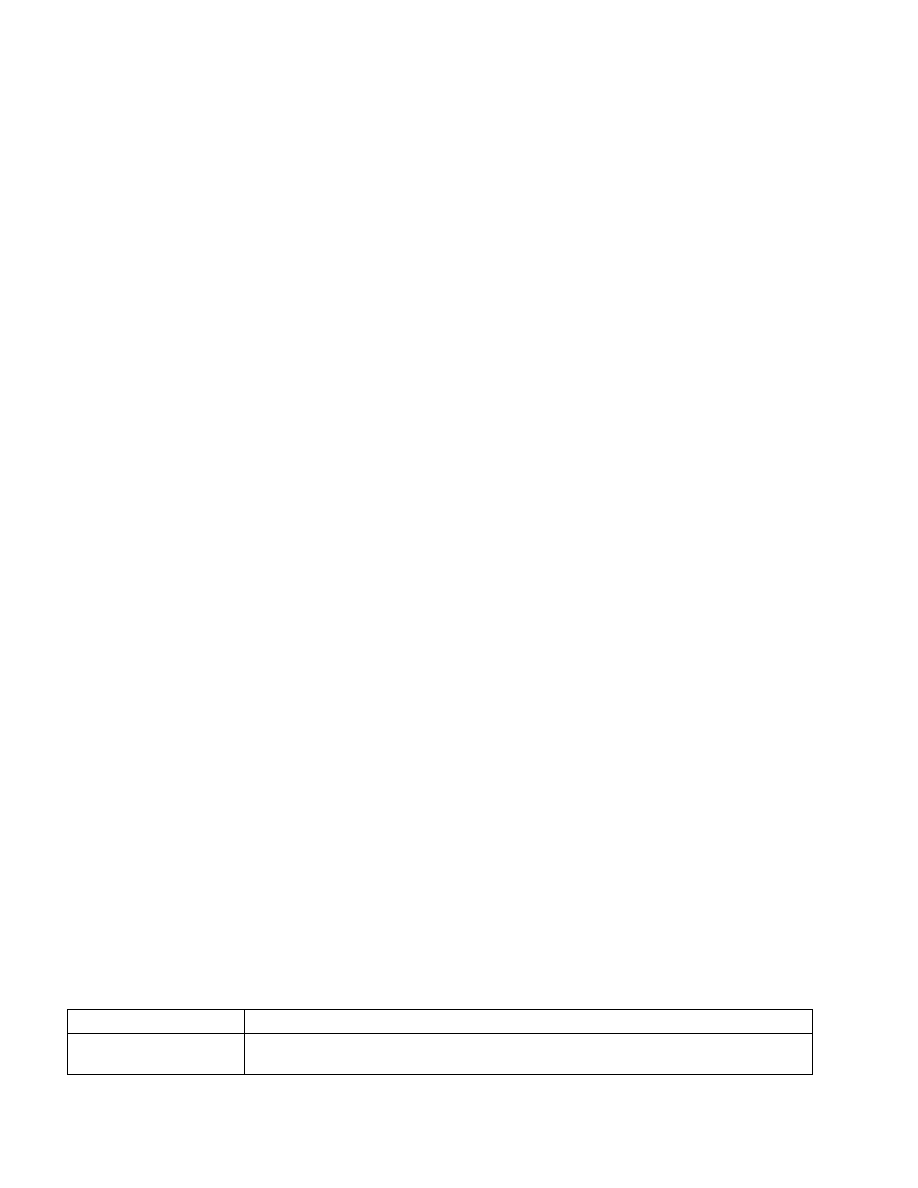

Table 36-1. COFI Type for Branch Instructions

COFI Type

Instructions

Conditional Branch

JA, JAE, JB, JBE, JC, JCXZ< JECXZ, JRCXZ, JE, JG, JGE, JL, JLE, JNA, JNAE, JNB, JNBE, JNC, JNE, JNG, JNGE,

JNL, JNLE, JNO, JNP, JNS, JNZ, JO, JP, JPE, JPO, JS, JZ, LOOP, LOOPE, LOOPNE, LOOPNZ, LOOPZ