35-314 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

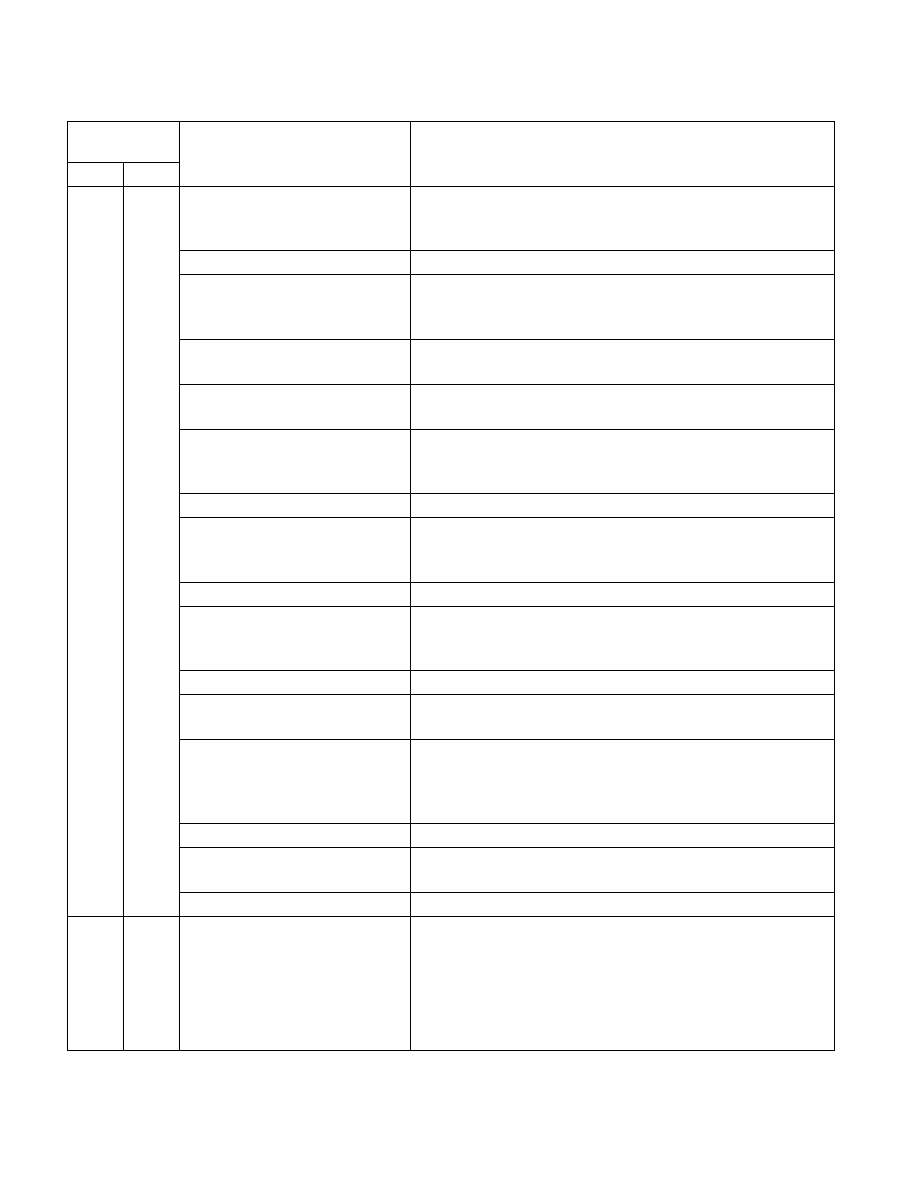

4

Address Parity Enable (R)

0 = Disabled

Always 0 on the Pentium M processor.

6:5

Reserved.

7

BINIT# Driver Enable (R)

1 = Enabled; 0 = Disabled

Always 0 on the Pentium M processor.

8

Output Tri-state Enabled (R/O)

1 = Enabled; 0 = Disabled

9

Execute BIST (R/O)

1 = Enabled; 0 = Disabled

10

MCERR# Observation Enabled (R/O)

1 = Enabled; 0 = Disabled

Always 0 on the Pentium M processor.

11

Reserved.

12

BINIT# Observation Enabled (R/O)

1 = Enabled; 0 = Disabled

Always 0 on the Pentium M processor.

13

Reserved.

14

1 MByte Power on Reset Vector (R/O)

1 = 1 MByte; 0 = 4 GBytes

Always 0 on the Pentium M processor.

15

Reserved.

17:16

APIC Cluster ID (R/O)

Always 00B on the Pentium M processor.

18

System Bus Frequency (R/O)

0 = 100 MHz

1 = Reserved

Always 0 on the Pentium M processor.

19

Reserved.

21: 20

Symmetric Arbitration ID (R/O)

Always 00B on the Pentium M processor.

26:22

Clock Frequency Ratio (R/O)

40H

64

MSR_LASTBRANCH_0

Last Branch Record 0 (R/W)

One of 8 last branch record registers on the last branch record stack: bits

31-0 hold the ‘from’ address and bits 63-32 hold the to address.

See also:

• Last Branch Record Stack TOS at 1C9H

• Section 17.13, “Last Branch, Interrupt, and Exception Recording

Table 35-45. MSRs in Pentium M Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec