Vol. 3C 35-309

MODEL-SPECIFIC REGISTERS (MSRS)

13

Shared

TM2 Enable (R/W)

When this bit is set (1) and the thermal sensor indicates that the

die temperature is at the pre-determined threshold, the Thermal

Monitor 2 mechanism is engaged. TM2 will reduce the bus to core

ratio and voltage according to the value last written to

MSR_THERM2_CTL bits 15:0.

When this bit is clear (0, default), the processor does not change

the VID signals or the bus to core ratio when the processor enters

a thermal managed state.

If the TM2 feature flag (ECX[8]) is not set to 1 after executing

CPUID with EAX = 1, then this feature is not supported and BIOS

must not alter the contents of this bit location. The processor is

operating out of spec if both this bit and the TM1 bit are set to

disabled states.

15:14

Reserved.

16

Shared

Enhanced Intel SpeedStep Technology Enable (R/W)

1 = Enhanced Intel SpeedStep Technology enabled

18

Shared

ENABLE MONITOR FSM (R/W)

See Table 35-2.

19

Reserved.

22

Shared

Limit CPUID Maxval (R/W)

See Table 35-2.

Setting this bit may cause behavior in software that depends on

the availability of CPUID leaves greater than 2.

33:23

Reserved.

34

Shared

XD Bit Disable (R/W)

See Table 35-2.

63:35

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Unique

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-3) that points to the MSR containing the

most recent branch record.

See MSR_LASTBRANCH_0_FROM_IP (at 40H).

1D9H

473

IA32_DEBUGCTL

Unique

Debug Control (R/W)

Controls how several debug features are used. Bit definitions are

discussed in the referenced section.

1DDH

477

MSR_LER_FROM_LIP Unique

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

1DEH

478

MSR_LER_TO_LIP

Unique

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch

instruction that the processor executed prior to the last exception

that was generated or the last interrupt that was handled.

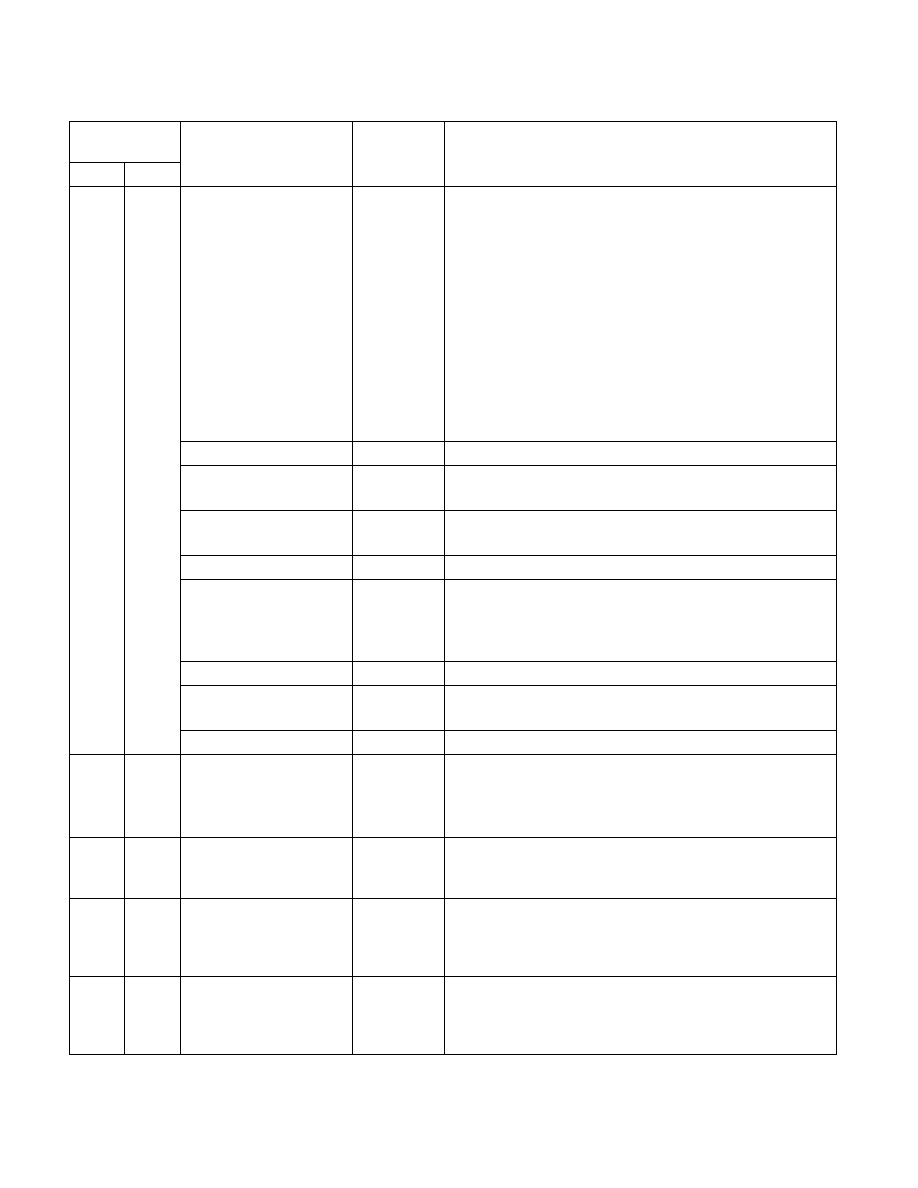

Table 35-44. MSRs in Intel® Core™ Solo, Intel® Core™ Duo Processors, and Dual-Core Intel® Xeon® Processor LV

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec