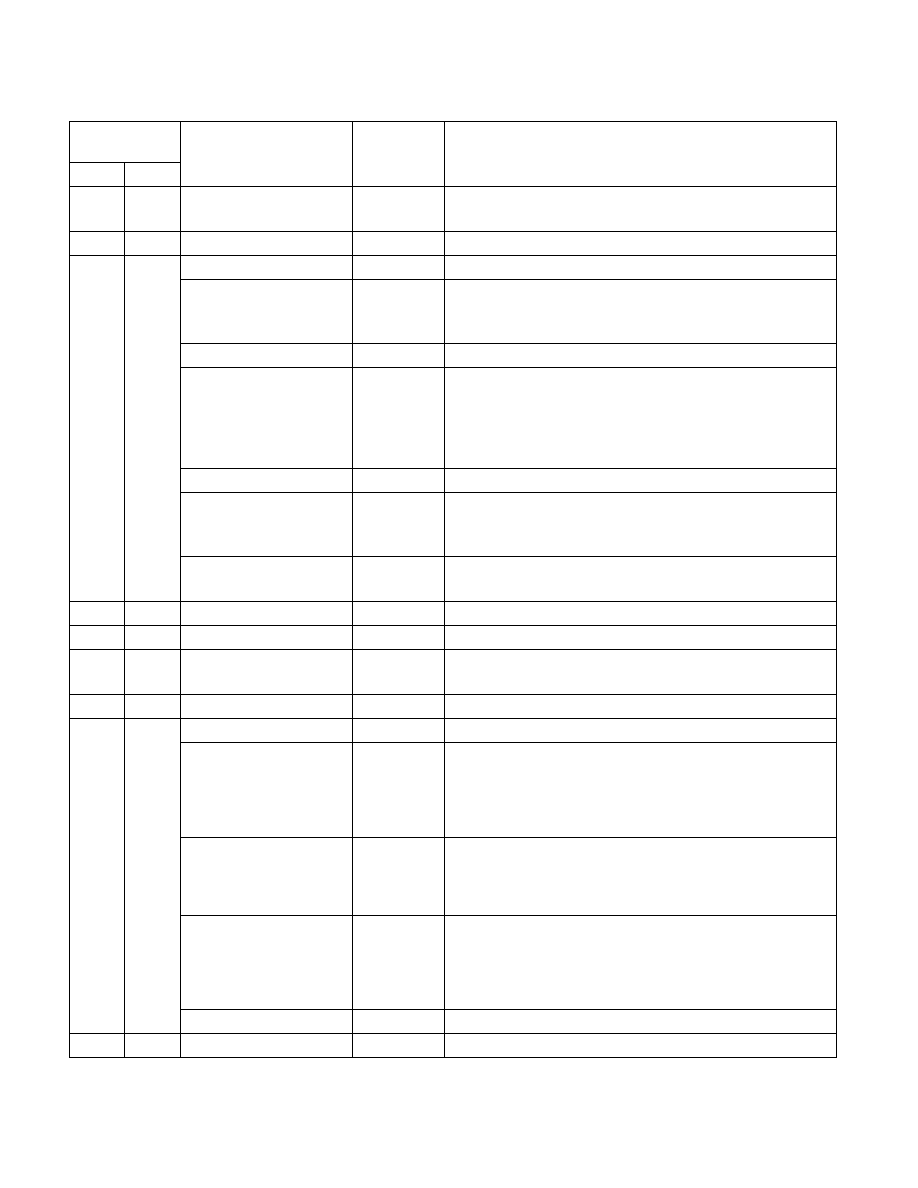

Vol. 3C 35-307

MODEL-SPECIFIC REGISTERS (MSRS)

E8H

232

IA32_APERF

Unique

Actual Performance Frequency Clock Count. (RW)

See Table 35-2.

FEH

254

IA32_MTRRCAP

Unique

11EH

281

MSR_BBL_CR_CTL3

Shared

0

L2 Hardware Enabled (RO)

1 = If the L2 is hardware-enabled

0 = Indicates if the L2 is hardware-disabled

7:1

Reserved.

8

L2 Enabled (R/W)

1 = L2 cache has been initialized

0 = Disabled (default)

Until this bit is set the processor will not respond to the WBINVD

instruction or the assertion of the FLUSH# input.

22:9

Reserved.

23

L2 Not Present (RO)

0 = L2 Present

1 = L2 Not Present

63:24

Reserved.

174H

372

IA32_SYSENTER_CS

Unique

175H

373

IA32_SYSENTER_ESP

Unique

See Table 35-2.

176H

374

IA32_SYSENTER_EIP

Unique

See Table 35-2.

179H

377

IA32_MCG_CAP

Unique

17AH

378

IA32_MCG_STATUS

Unique

0

RIPV

When set, this bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check

was generated) can be used to restart the program. If this bit is

cleared, the program cannot be reliably restarted.

1

EIPV

When set, this bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check

was generated) is directly associated with the error.

2

MCIP

When set, this bit indicates that a machine check has been

generated. If a second machine check is detected while this bit is

still set, the processor enters a shutdown state. Software should

write this bit to 0 after processing a machine check exception.

63:3

Reserved.

186H

390

IA32_PERFEVTSEL0

Unique

See Table 35-2.

Table 35-44. MSRs in Intel® Core™ Solo, Intel® Core™ Duo Processors, and Dual-Core Intel® Xeon® Processor LV

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec