35-288 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

Single processor platforms should not set this bit.

Server platforms should set or clear this bit based

on platform performance observed in validation

and testing.

BIOS may contain a setup option that controls the

setting of this bit.

21:20

Reserved.

22

3, 4, 6

Limit CPUID MAXVAL (R/W)

See Table 35-2.

Setting this can cause unexpected behavior to

software that depends on the availability of CPUID

leaves greater than 3.

23

Shared

xTPR Message Disable (R/W)

See Table 35-2.

24

L1 Data Cache Context Mode (R/W)

When set, the L1 data cache is placed in shared

mode; when clear (default), the cache is placed in

adaptive mode. This bit is only enabled for IA-32

processors that support Intel Hyper-Threading

Technology. See Section 11.5.6, “L1 Data Cache

Context Mode.”

When L1 is running in adaptive mode and CR3s

are identical, data in L1 is shared across logical

processors. Otherwise, L1 is not shared and cache

use is competitive.

If the Context ID feature flag (ECX[10]) is set to 0

after executing CPUID with EAX = 1, the ability to

switch modes is not supported. BIOS must not

alter the contents of IA32_MISC_ENABLE[24].

33:25

Reserved.

34

Unique

XD Bit Disable (R/W)

See Table 35-2.

63:35

Reserved.

1A1H

417

MSR_PLATFORM_BRV

3, 4, 6

Shared

Platform Feature Requirements (R)

17:0

Reserved.

18

PLATFORM Requirements

When set to 1, indicates the processor has specific

platform requirements. The details of the platform

requirements are listed in the respective data

sheets of the processor.

63:19

Reserved.

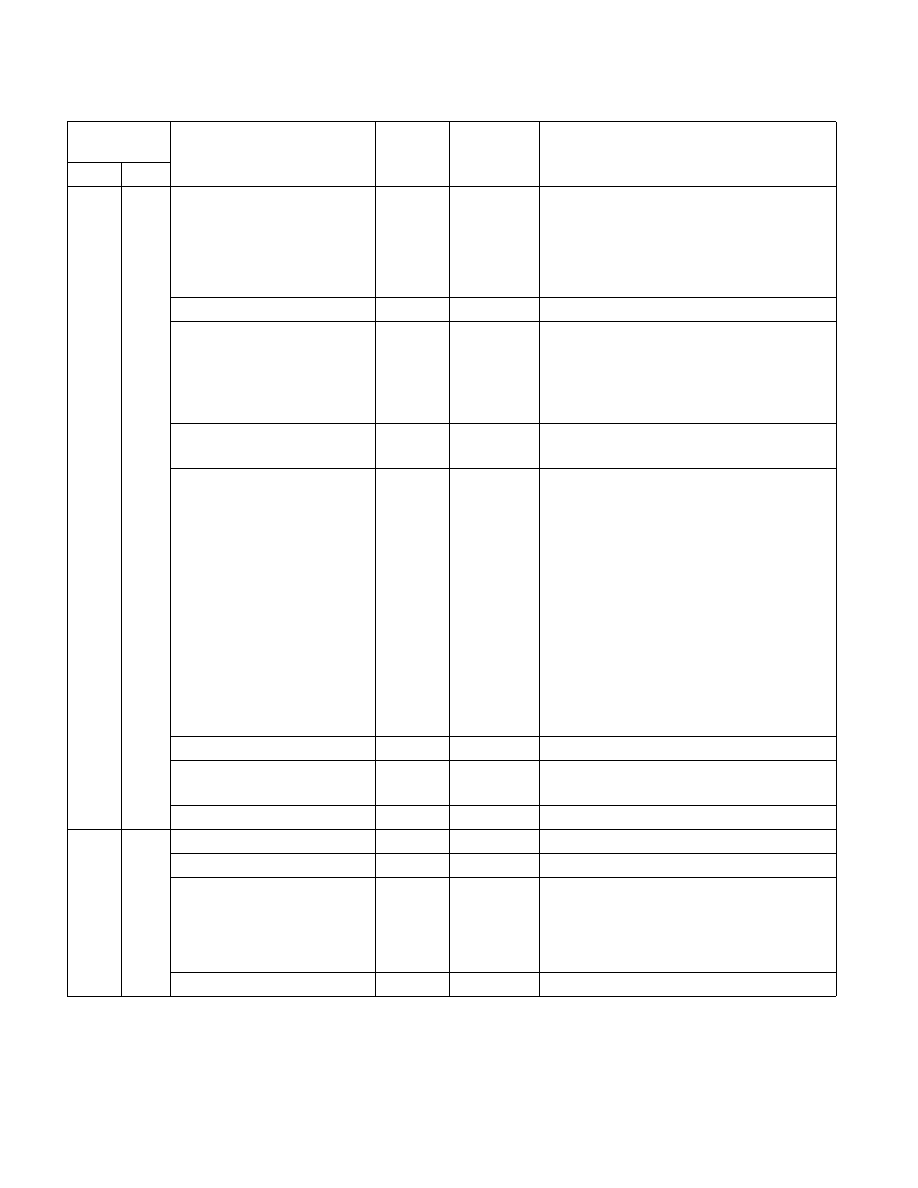

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec