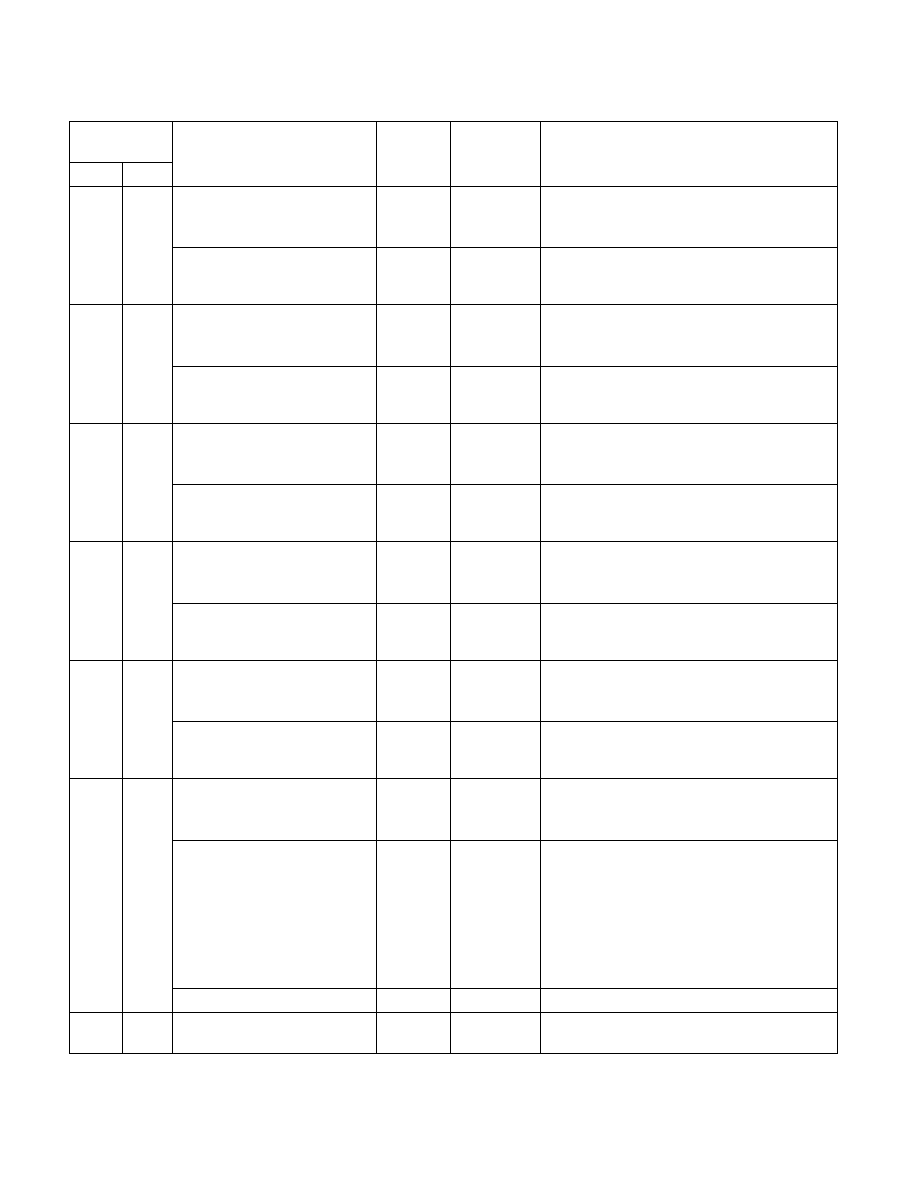

Vol. 3C 35-283

MODEL-SPECIFIC REGISTERS (MSRS)

185H

389

MSR_MCG_RDI

0, 1, 2, 3,

4, 6

Unique

Machine Check EDI/RDI Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

186H

390

MSR_MCG_RBP

0, 1, 2, 3,

4, 6

Unique

Machine Check EBP/RBP Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

187H

391

MSR_MCG_RSP

0, 1, 2, 3,

4, 6

Unique

Machine Check ESP/RSP Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

188H

392

MSR_MCG_RFLAGS

0, 1, 2, 3,

4, 6

Unique

Machine Check EFLAGS/RFLAG Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

189H

393

MSR_MCG_RIP

0, 1, 2, 3,

4, 6

Unique

Machine Check EIP/RIP Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

18AH

394

MSR_MCG_MISC

0, 1, 2, 3,

4, 6

Unique

Machine Check Miscellaneous

See Section 15.3.2.6, “IA32_MCG Extended

0

DS

When set, the bit indicates that a page assist or

page fault occurred during DS normal operation.

The processors response is to shut down.

The bit is used as an aid for debugging DS

handling code. It is the responsibility of the user

(BIOS or operating system) to clear this bit for

normal operation.

63:1

Reserved.

18BH -

18FH

395

MSR_MCG_RESERVED1 -

MSR_MCG_RESERVED5

Reserved.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec