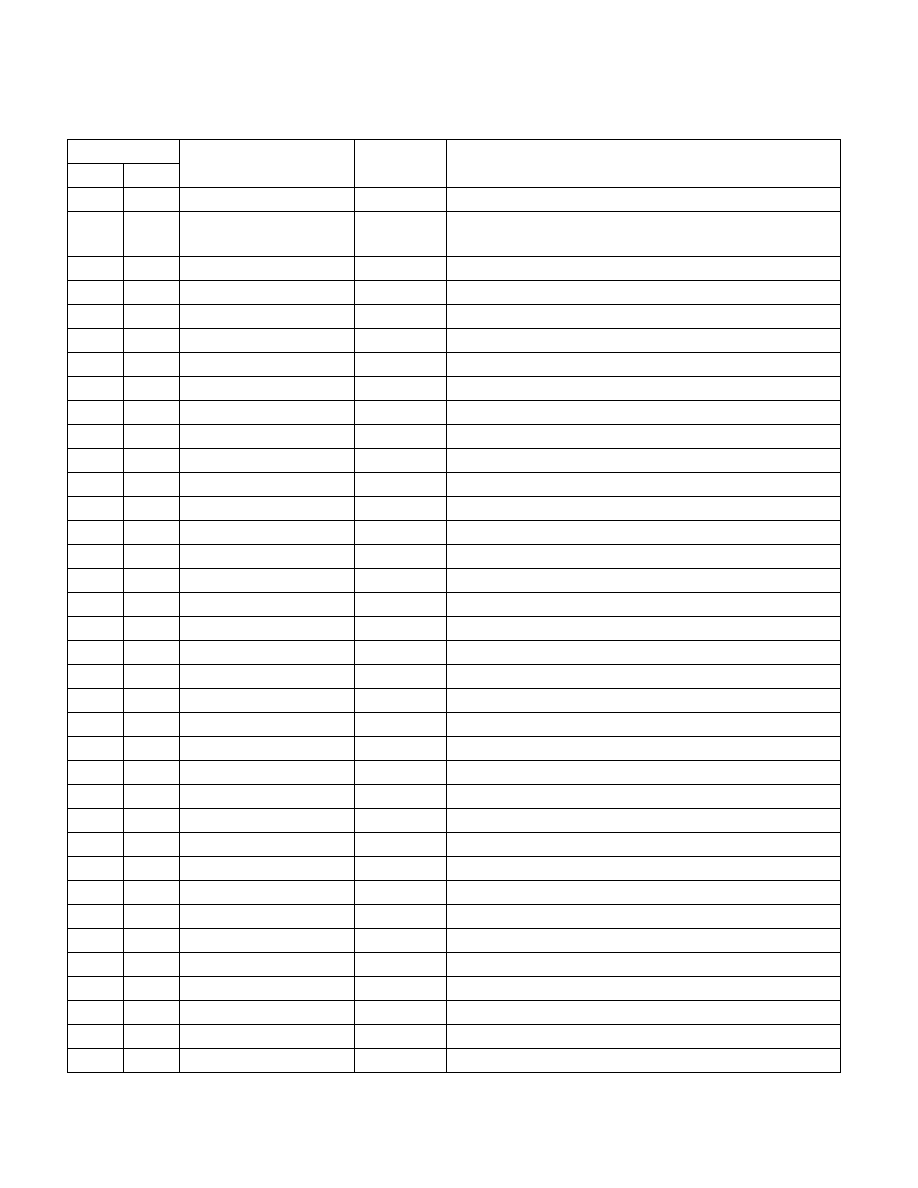

35-276 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

63:9

Reserved.

6E0H

1760

IA32_TSC_DEADLINE

Core

TSC Target of Local APIC’s TSC Deadline Mode (R/W)

See Table 35-2

802H

2050

IA32_X2APIC_APICID

Thread

x2APIC ID register (R/O) See x2APIC Specification.

803H

2051

IA32_X2APIC_VERSION

Thread

x2APIC Version register (R/O)

808H

2056

IA32_X2APIC_TPR

Thread

x2APIC Task Priority register (R/W)

80AH

2058

IA32_X2APIC_PPR

Thread

x2APIC Processor Priority register (R/O)

80BH

2059

IA32_X2APIC_EOI

Thread

x2APIC EOI register (W/O)

80DH

2061

IA32_X2APIC_LDR

Thread

x2APIC Logical Destination register (R/O)

80FH

2063

IA32_X2APIC_SIVR

Thread

x2APIC Spurious Interrupt Vector register (R/W)

810H

2064

IA32_X2APIC_ISR0

Thread

x2APIC In-Service register bits [31:0] (R/O)

811H

2065

IA32_X2APIC_ISR1

Thread

x2APIC In-Service register bits [63:32] (R/O)

812H

2066

IA32_X2APIC_ISR2

Thread

x2APIC In-Service register bits [95:64] (R/O)

813H

2067

IA32_X2APIC_ISR3

Thread

x2APIC In-Service register bits [127:96] (R/O)

814H

2068

IA32_X2APIC_ISR4

Thread

x2APIC In-Service register bits [159:128] (R/O)

815H

2069

IA32_X2APIC_ISR5

Thread

x2APIC In-Service register bits [191:160] (R/O)

816H

2070

IA32_X2APIC_ISR6

Thread

x2APIC In-Service register bits [223:192] (R/O)

817H

2071

IA32_X2APIC_ISR7

Thread

x2APIC In-Service register bits [255:224] (R/O)

818H

2072

IA32_X2APIC_TMR0

Thread

x2APIC Trigger Mode register bits [31:0] (R/O)

819H

2073

IA32_X2APIC_TMR1

Thread

x2APIC Trigger Mode register bits [63:32] (R/O)

81AH

2074

IA32_X2APIC_TMR2

Thread

x2APIC Trigger Mode register bits [95:64] (R/O)

81BH

2075

IA32_X2APIC_TMR3

Thread

x2APIC Trigger Mode register bits [127:96] (R/O)

81CH

2076

IA32_X2APIC_TMR4

Thread

x2APIC Trigger Mode register bits [159:128] (R/O)

81DH

2077

IA32_X2APIC_TMR5

Thread

x2APIC Trigger Mode register bits [191:160] (R/O)

81EH

2078

IA32_X2APIC_TMR6

Thread

x2APIC Trigger Mode register bits [223:192] (R/O)

81FH

2079

IA32_X2APIC_TMR7

Thread

x2APIC Trigger Mode register bits [255:224] (R/O)

820H

2080

IA32_X2APIC_IRR0

Thread

x2APIC Interrupt Request register bits [31:0] (R/O)

821H

2081

IA32_X2APIC_IRR1

Thread

x2APIC Interrupt Request register bits [63:32] (R/O)

822H

2082

IA32_X2APIC_IRR2

Thread

x2APIC Interrupt Request register bits [95:64] (R/O)

823H

2083

IA32_X2APIC_IRR3

Thread

x2APIC Interrupt Request register bits [127:96] (R/O)

824H

2084

IA32_X2APIC_IRR4

Thread

x2APIC Interrupt Request register bits [159:128] (R/O)

825H

2085

IA32_X2APIC_IRR5

Thread

x2APIC Interrupt Request register bits [191:160] (R/O)

826H

2086

IA32_X2APIC_IRR6

Thread

x2APIC Interrupt Request register bits [223:192] (R/O)

827H

2087

IA32_X2APIC_IRR7

Thread

x2APIC Interrupt Request register bits [255:224] (R/O)

828H

2088

IA32_X2APIC_ESR

Thread

x2APIC Error Status register (R/W)

82FH

2095

IA32_X2APIC_LVT_CMCI

Thread

x2APIC LVT Corrected Machine Check Interrupt register (R/W)

830H

2096

IA32_X2APIC_ICR

Thread

x2APIC Interrupt Command register (R/W)

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec