Vol. 3C 35-271

MODEL-SPECIFIC REGISTERS (MSRS)

63:61

Package

Group Ratio Delta for Group 6

An unsigned integer specifying the ratio decrement relative to the

Max ratio limit for Group 5.

1B0H

432

IA32_ENERGY_PERF_BIAS

Thread

1B1H

433

IA32_PACKAGE_THERM_

STATUS

Package

See Table 35-2.

1B2H

434

IA32_PACKAGE_THERM_

INTERRUPT

Package

See Table 35-2.

1C8H

456

MSR_LBR_SELECT

Thread

Last Branch Record Filtering Select Register (R/W)

1C9H

457

MSR_LASTBRANCH_TOS

Thread

Last Branch Record Stack TOS (R/W)

1D9H

473

IA32_DEBUGCTL

Thread

Debug Control (R/W)

See Table 35-2.

1DDH

477

MSR_LER_FROM_LIP Thread

Last Exception Record From Linear IP (R)

1DEH

478

MSR_LER_TO_LIP

Thread

Last Exception Record To Linear IP (R)

1F2H

498

IA32_SMRR_PHYSBASE

Core

See Table 35-2.

1F3H

499

IA32_SMRR_PHYSMASK

Core

See Table 35-2.

200H

512

IA32_MTRR_PHYSBASE0

Core

See Table 35-2.

201H

513

IA32_MTRR_PHYSMASK0

Core

See Table 35-2.

202H

514

IA32_MTRR_PHYSBASE1

Core

See Table 35-2.

203H

515

IA32_MTRR_PHYSMASK1

Core

See Table 35-2.

204H

516

IA32_MTRR_PHYSBASE2

Core

See Table 35-2.

205H

517

IA32_MTRR_PHYSMASK2

Core

See Table 35-2.

206H

518

IA32_MTRR_PHYSBASE3

Core

See Table 35-2.

207H

519

IA32_MTRR_PHYSMASK3

Core

See Table 35-2.

208H

520

IA32_MTRR_PHYSBASE4

Core

See Table 35-2.

209H

521

IA32_MTRR_PHYSMASK4

Core

See Table 35-2.

20AH

522

IA32_MTRR_PHYSBASE5

Core

See Table 35-2.

20BH

523

IA32_MTRR_PHYSMASK5

Core

20CH

524

IA32_MTRR_PHYSBASE6

Core

20DH

525

IA32_MTRR_PHYSMASK6

Core

20EH

526

IA32_MTRR_PHYSBASE7

Core

20FH

527

IA32_MTRR_PHYSMASK7

Core

250H

592

IA32_MTRR_FIX64K_00000 Core

See Table 35-2.

258H

600

IA32_MTRR_FIX16K_80000 Core

See Table 35-2.

259H

601

IA32_MTRR_FIX16K_A000

0

Core

268H

616

IA32_MTRR_FIX4K_C0000

Core

269H

617

IA32_MTRR_FIX4K_C8000

Core

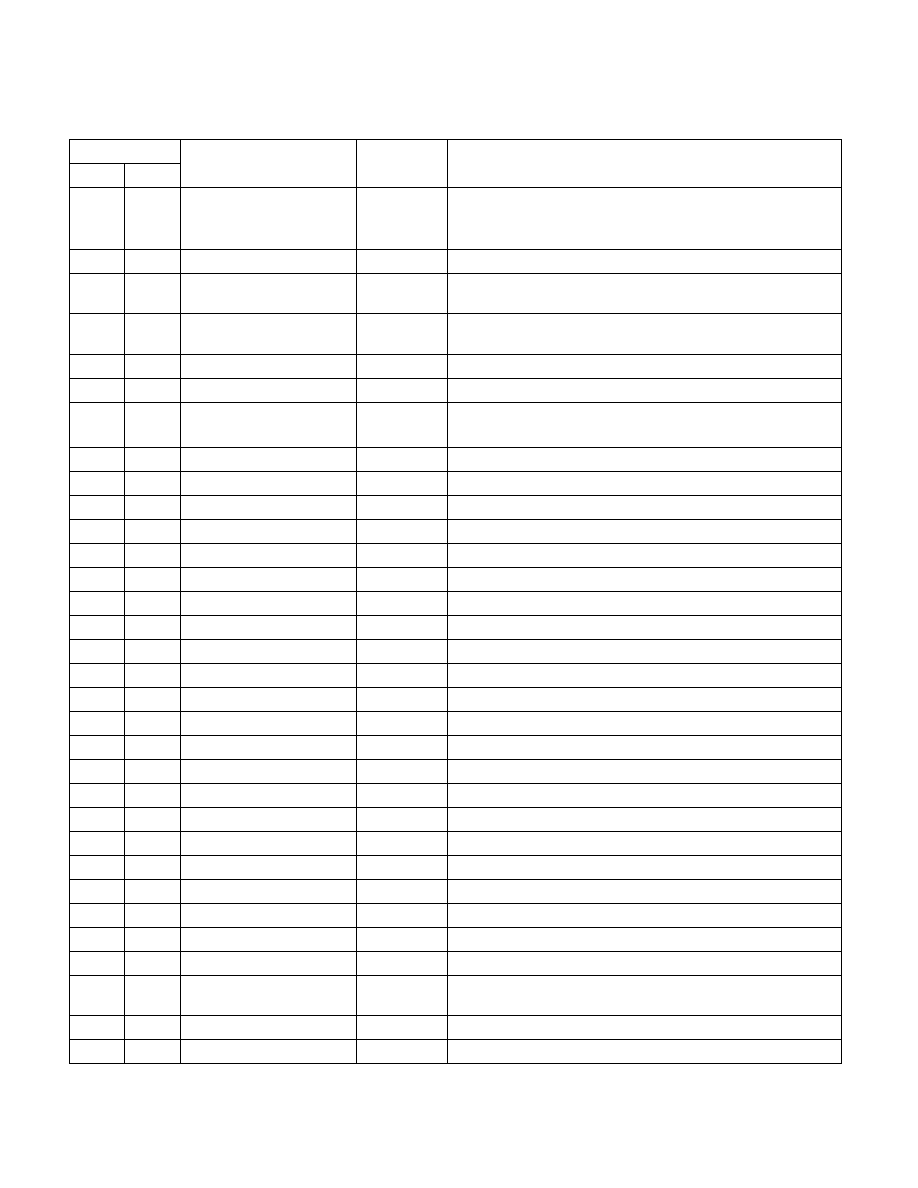

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec