35-268 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

31:24

CMASK

63:32

Reserved.

187H

391

IA32_PERFEVTSEL1

Thread

See Table 35-2.

198H

408

IA32_PERF_STATUS

Package

See Table 35-2.

199H

409

IA32_PERF_CTL

Thread

See Table 35-2.

19AH

410

IA32_CLOCK_MODULATION

Thread

Clock Modulation (R/W)

See Table 35-2.

19BH

411

IA32_THERM_INTERRUPT

Module

Thermal Interrupt Control (R/W)

See Table 35-2.

19CH

412

IA32_THERM_STATUS

Module

Thermal Monitor Status (R/W)

See Table 35-2.

0

Thermal status (RO)

1

Thermal status log (R/WC0)

2

PROTCHOT # or FORCEPR# status (RO)

3

PROTCHOT # or FORCEPR# log (R/WC0)

4

Critical Temperature status (RO)

5

Critical Temperature status log (R/WC0)

6

Thermal threshold #1 status (RO)

7

Thermal threshold #1 log (R/WC0)

8

Thermal threshold #2 status (RO)

9

Thermal threshold #2 log (R/WC0)

10

Power Limitation status (RO)

11

Power Limitation log (R/WC0)

15:12

Reserved.

22:16

Digital Readout (RO)

26:23

Reserved.

30:27

Resolution in degrees Celsius (RO)

31

Reading Valid (RO)

63:32

Reserved.

1A0H

416

IA32_MISC_ENABLE

Thread

Enable Misc. Processor Features (R/W)

Allows a variety of processor functions to be enabled and disabled.

0

Fast-Strings Enable

2:1

Reserved.

3

Automatic Thermal Control Circuit Enable (R/W) Default value is

1.

6:4

Reserved.

7

Performance Monitoring Available (R)

10:8

Reserved.

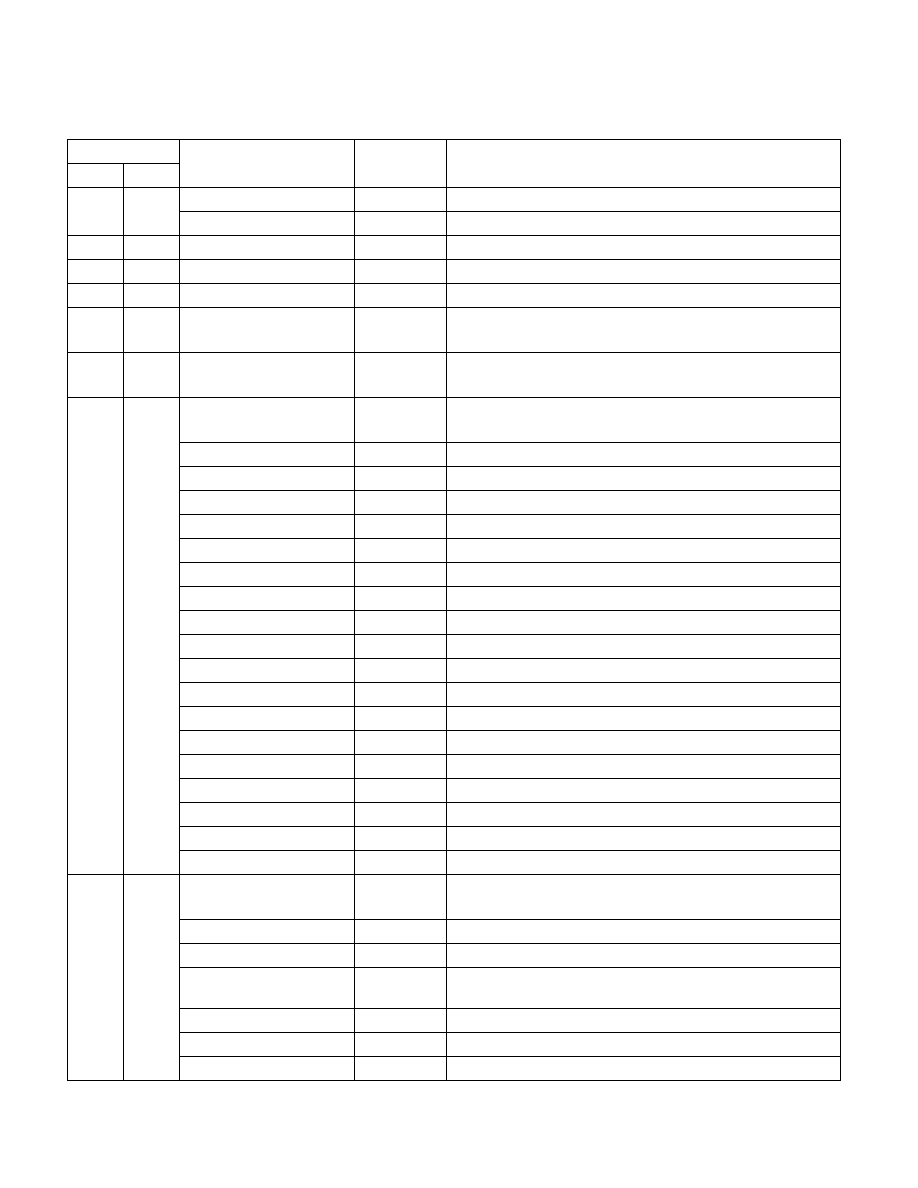

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec