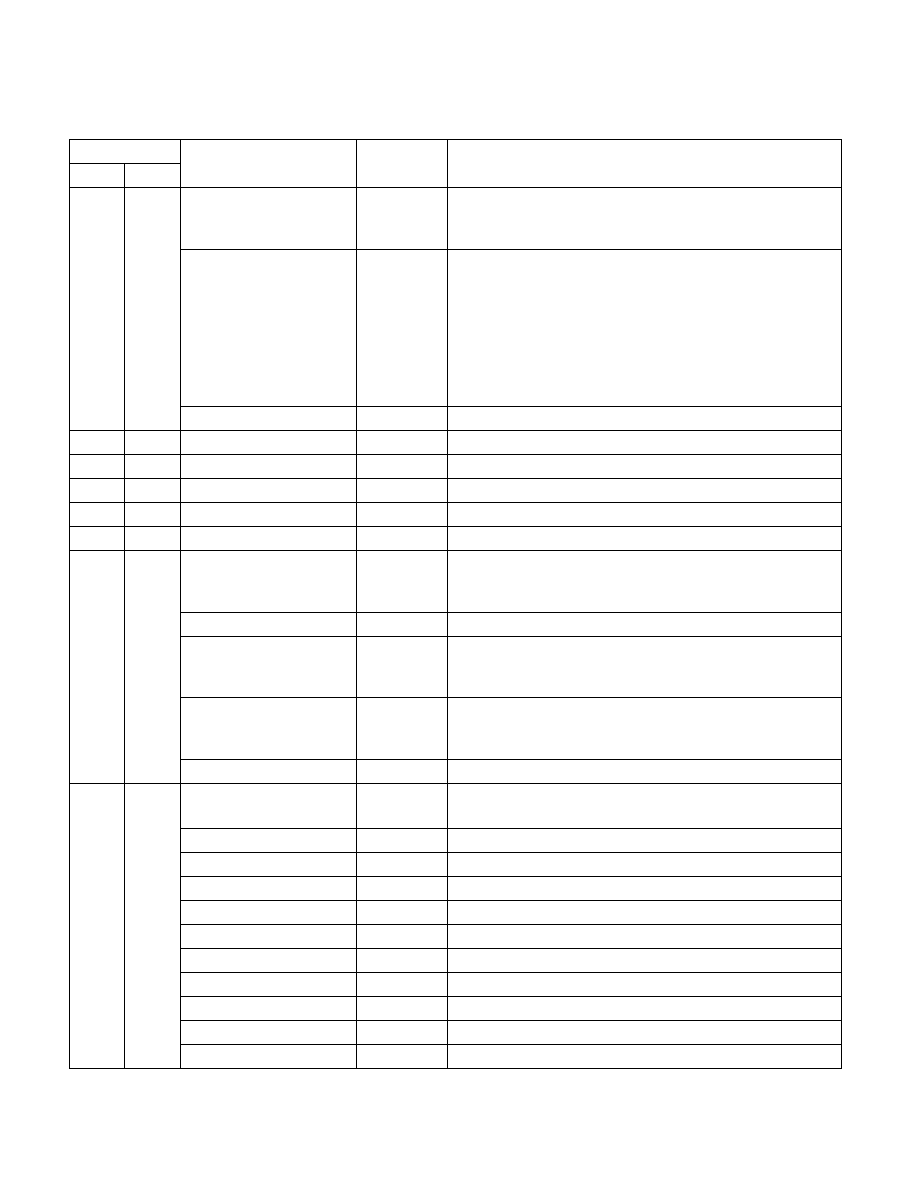

Vol. 3C 35-267

MODEL-SPECIFIC REGISTERS (MSRS)

13CH

52

MSR_FEATURE_CONFIG

Core

AES Configuration (RW-L)

Privileged post-BIOS agent must provide a #GP handler to handle

unsuccessful read of this MSR.

1:0

AES Configuration (RW-L)

Upon a successful read of this MSR, the configuration of AES

instruction set availability is as follows:

11b: AES instructions are not available until next RESET.

otherwise, AES instructions are available.

Note, AES instruction set is not available if read is unsuccessful. If

the configuration is not 01b, AES instruction can be mis-configured

if a privileged agent unintentionally writes 11b.

63:2

Reserved.

174H

372

IA32_SYSENTER_CS

Thread

175H

373

IA32_SYSENTER_ESP

Thread

See Table 35-2.

176H

374

IA32_SYSENTER_EIP

Thread

See Table 35-2.

179H

377

IA32_MCG_CAP

Thread

17AH

378

IA32_MCG_STATUS

Thread

See Table 35-2.

17DH

390

MSR_SMM_MCA_CAP

THREAD

Enhanced SMM Capabilities (SMM-RO)

Reports SMM capability Enhancement. Accessible only while in

SMM.

57:0

Reserved

58

SMM_Code_Access_Chk (SMM-RO)

If set to 1 indicates that the SMM code access restriction is

supported and a host-space interface available to SMM handler.

59

Long_Flow_Indication (SMM-RO)

If set to 1 indicates that the SMM long flow indicator is supported

and a host-space interface available to SMM handler.

63:60

Reserved

186H

390

IA32_PERFEVTSEL0

Thread

Performance Monitoring Event Select Register (R/W)

See Table 35-2.

7:0

Event Select

15:8

UMask

16

USR

17

OS

18

Edge

19

PC

20

INT

21

AnyThread

22

EN

23

INV

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec