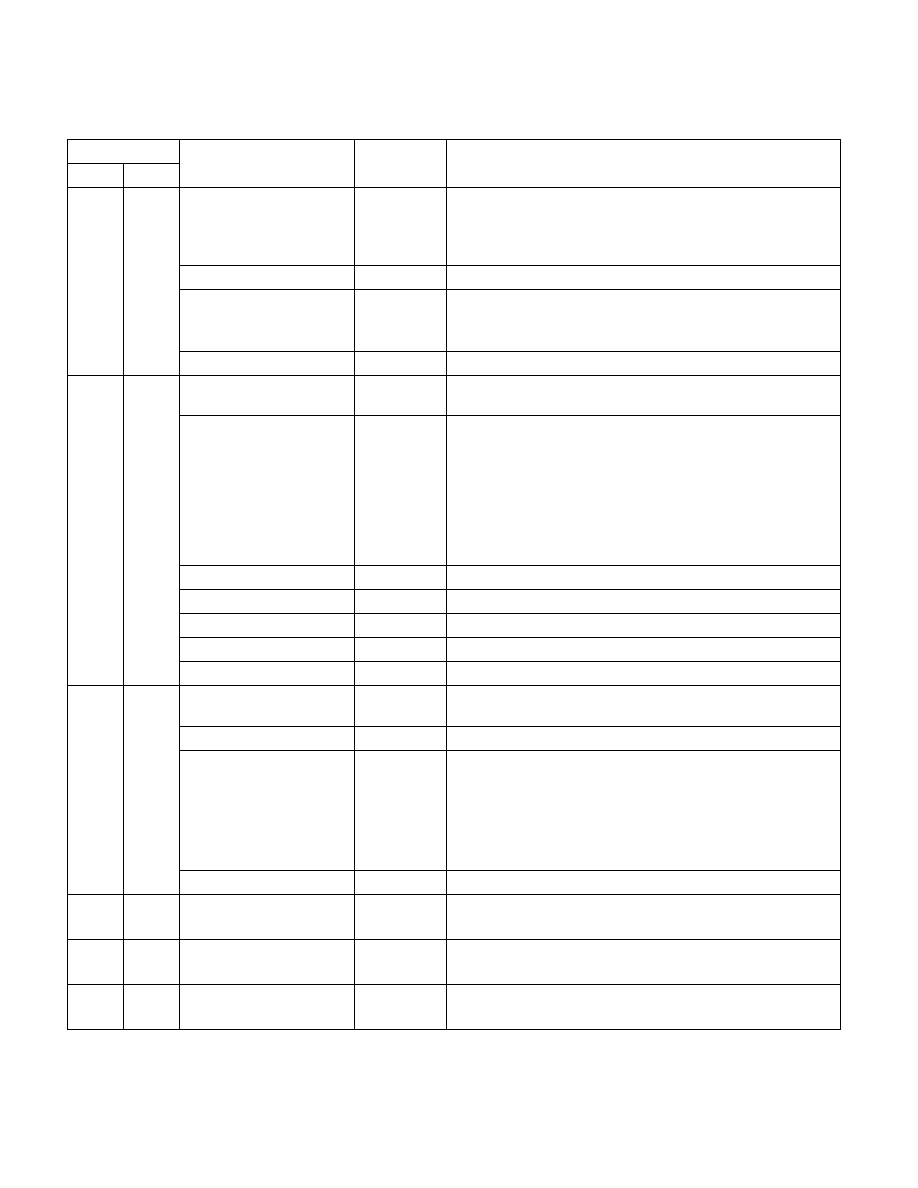

35-266 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

When set to 1, indicates that TDP Limits for Turbo mode are

programmable, and when set to 0, indicates TDP Limit for Turbo

mode is not programmable.

39:30

Reserved.

47:40

Package

Maximum Efficiency Ratio (R/O)

The is the minimum ratio (maximum efficiency) that the processor

can operates, in units of 100MHz.

63:48

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Module

C-State Configuration Control (R/W)

2:0

Package C-State Limit (R/W)

The following C-state code name encodings are supported:

000b: C0/C1

001b: C2

010b: C6 No Retention

011b: C6 Retention

111b: No limit

9:3

Reserved.

10

I/O MWAIT Redirection Enable (R/W)

14:11

Reserved.

15

CFG Lock (R/WO)

63:16

Reserved.

E4H

228

MSR_PMG_IO_CAPTURE_

BASE

Module

Power Management IO Redirection in C-state (R/W)

15:0

LVL_2 Base Address (R/W)

18:16

C-state Range (R/W)

Specifies the encoding value of the maximum C-State code name to

be included when IO read to MWAIT redirection is enabled by

MSR_PKG_CST_CONFIG_CONTROL[bit10]:

100b - C4 is the max C-State to include

110b - C6 is the max C-State to include

63:19

Reserved.

E7H

231

IA32_MPERF

Thread

Maximum Performance Frequency Clock Count (RW)

See Table 35-2.

E8H

232

IA32_APERF

Thread

Actual Performance Frequency Clock Count (RW)

See Table 35-2.

FEH

254

IA32_MTRRCAP

Core

Memory Type Range Register (R)

See Table 35-2.

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec