Vol. 3C 35-243

MODEL-SPECIFIC REGISTERS (MSRS)

12

Current Limit status (RO)

See Table 35-2.

13

Current Limit log (R/WC0)

See Table 35-2.

14

Cross Domain Limit status (RO)

See Table 35-2.

15

Cross Domain Limit log (R/WC0)

See Table 35-2.

22:16

Digital Readout (RO)

See Table 35-2.

26:23

Reserved.

30:27

Resolution in degrees Celsius (RO)

See Table 35-2.

31

Reading Valid (RO)

See Table 35-2.

63:32

Reserved.

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

23:16

Package

Maximum Ratio Limit for 3C

Maximum turbo ratio limit of 3 core active.

31:24

Package

Maximum Ratio Limit for 4C

Maximum turbo ratio limit of 4 core active.

63:32

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Thread

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-4) that points to the MSR containing the

most recent branch record.

300H

768

MSR_SGXOWNER0

Package

Lower 64 Bit OwnerEpoch Component of SGX Key (RO).

63:0

Low 64 bits of an 128-bit external entropy value for key

derivation of an enclave.

301H

768

MSR_SGXOWNER1

Package

Upper 64 Bit OwnerEpoch Component of SGX Key (RO).

63:0

Upper 64 bits of an 128-bit external entropy value for key

derivation of an enclave.

38EH

910

IA32_PERF_GLOBAL_

STATUS

See Table 35-2. See Section 18.2.2.3, “Full-Width Writes to

Performance Counter Registers.”

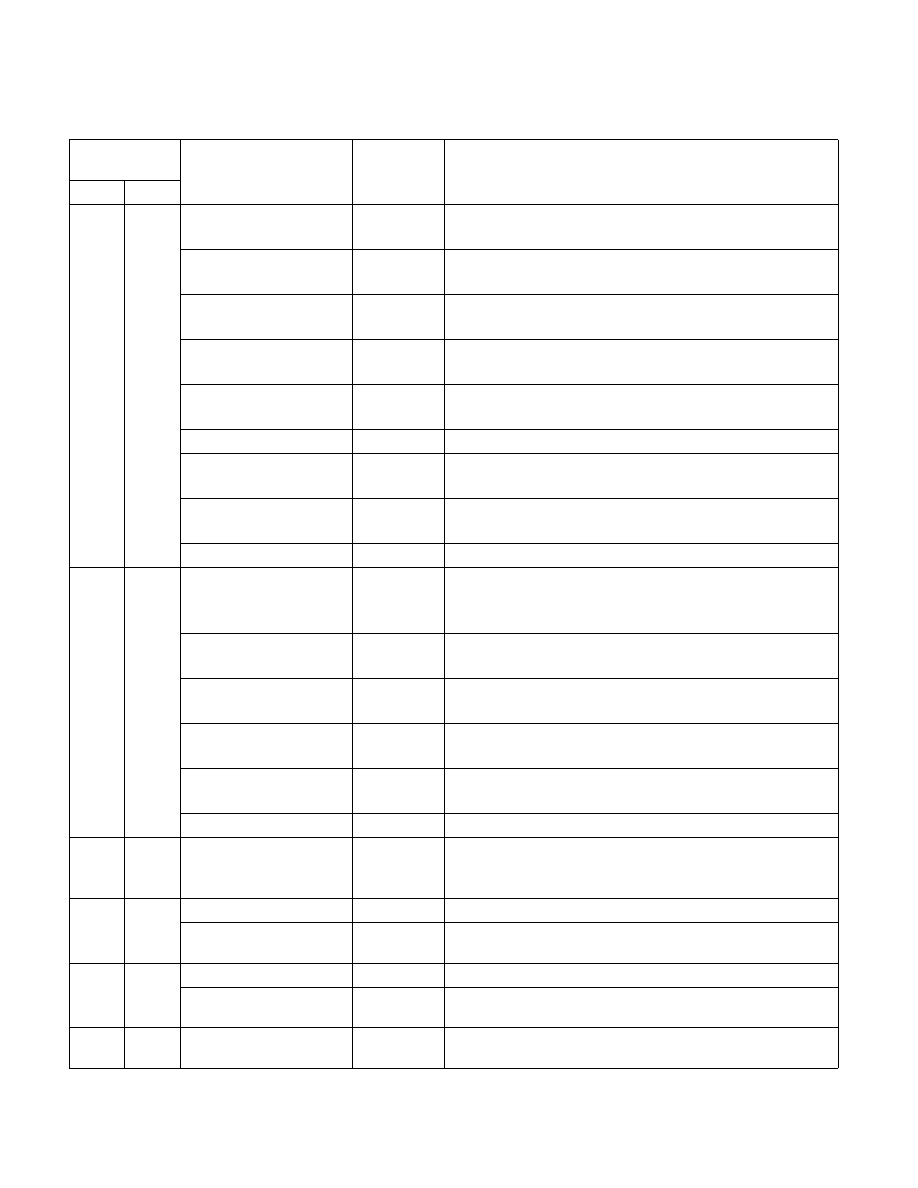

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec