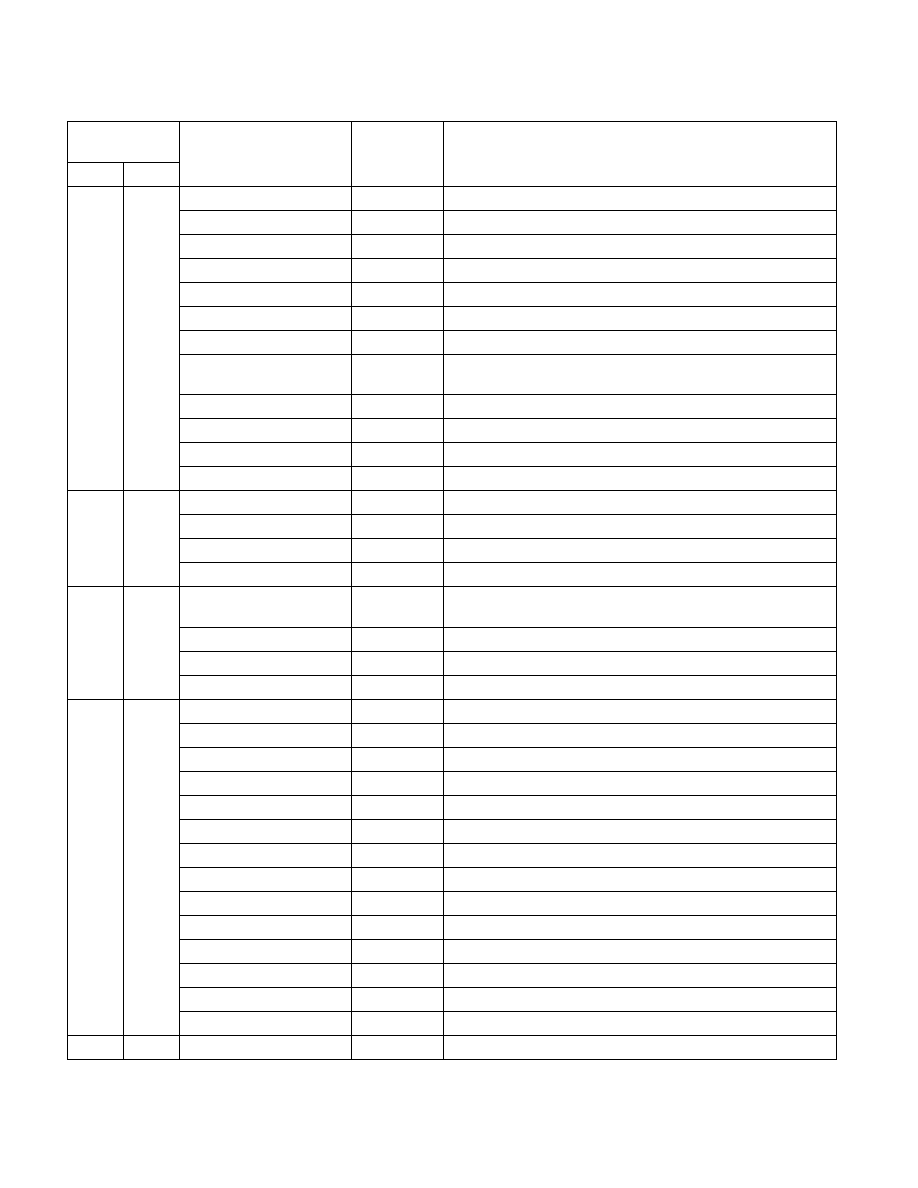

35-224 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

2

Set 1 to clear Ovf_PMC2

3

Set 1 to clear Ovf_PMC3

31:4

Reserved.

32

Set 1 to clear Ovf_FixedCtr0

33

Set 1 to clear Ovf_FixedCtr1

34

Set 1 to clear Ovf_FixedCtr2

54:35

Reserved.

55

Set 1 to clear Trace_ToPA_PMI. See Section 36.2.6.2, “Table of

60:56

Reserved.

61

Set 1 to clear Ovf_Uncore

62

Set 1 to clear Ovf_BufDSSAVE

63

Set 1 to clear CondChgd

560H

1376

IA32_RTIT_OUTPUT_BASE

THREAD

Trace Output Base Register (R/W)

6:0

Reserved.

MAXPHYADDR

1

-1:7

Base physical address.

63:MAXPHYADDR

Reserved.

561H

1377

IA32_RTIT_OUTPUT_MASK

_PTRS

THREAD

Trace Output Mask Pointers Register (R/W)

6:0

Reserved.

31:7

MaskOrTableOffset

63:32

Output Offset.

570H

1392

IA32_RTIT_CTL

Thread

Trace Control Register (R/W)

0

TraceEn

1

Reserved, MBZ.

2

OS

3

User

6:4

Reserved, MBZ

7

CR3 filter

8

ToPA; writing 0 will #GP if also setting TraceEn

9

Reserved, MBZ

10

TSCEn

11

DisRETC

12

Reserved, MBZ

13

Reserved; writing 0 will #GP if also setting TraceEn

63:14

Reserved, MBZ.

571H

1393

IA32_RTIT_STATUS

Thread

Tracing Status Register (R/W)

Table 35-32. Additional MSRs Common to Processors Based the Broadwell Microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec