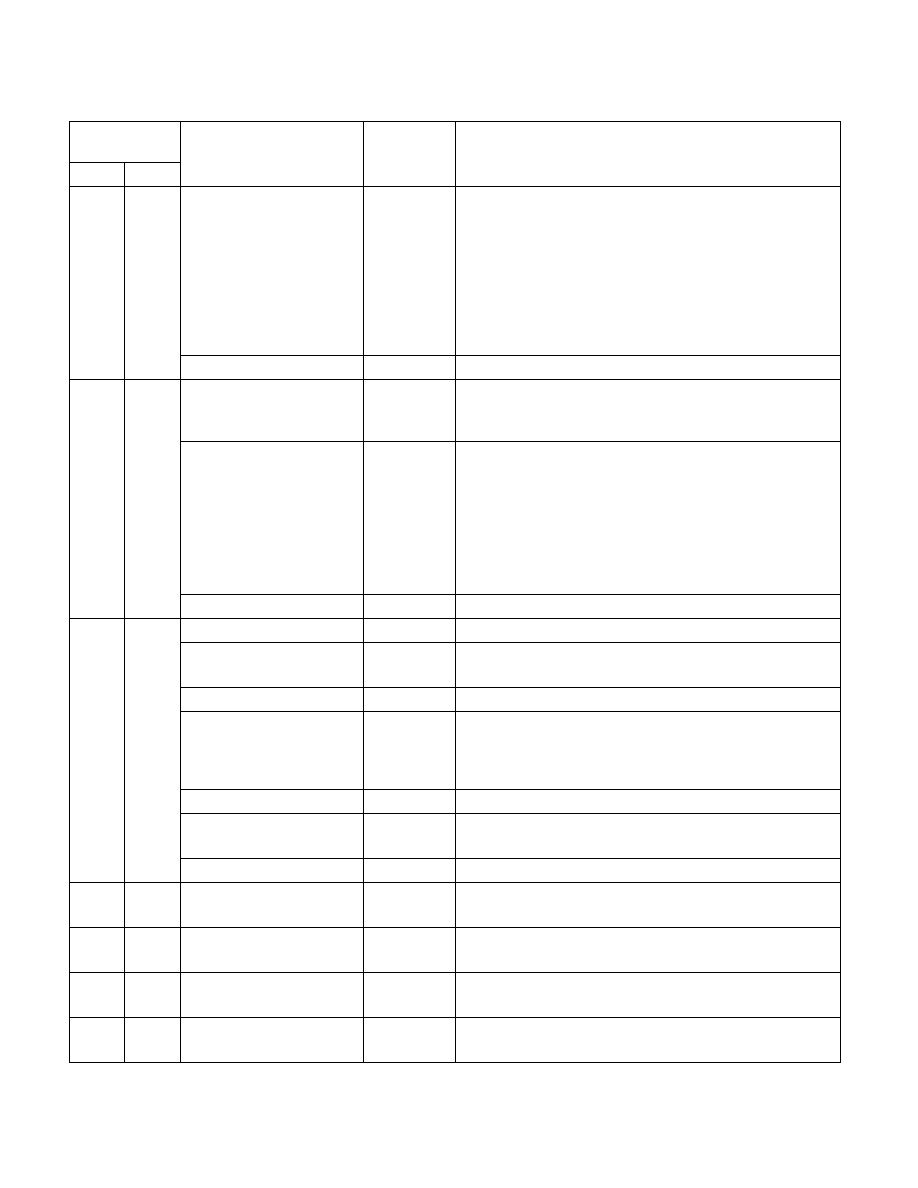

Vol. 3C 35-197

MODEL-SPECIFIC REGISTERS (MSRS)

N-1:0

LOG_PROC_STATE (SMM-RO)

Each bit represents a logical processor of its state in a long flow of

internal operation which delays servicing an interrupt. The

corresponding bit will be set at the start of long events such as:

Microcode Update Load, C6, WBINVD, Ratio Change, Throttle.

The bit is automatically cleared at the end of each long event. The

reset value of this field is 0.

Only bit positions below N = CPUID.(EAX=0BH,

ECX=PKG_LVL):EBX[15:0] can be updated.

63:N

Reserved

4E3H

1251

MSR_SMM_BLOCKED

Package

SMM Blocked (SMM-RO)

Reports the blocked state of all logical processors in the package.

Available only while in SMM.

N-1:0

LOG_PROC_STATE (SMM-RO)

Each bit represents a logical processor of its blocked state to

service an SMI. The corresponding bit will be set if the logical

processor is in one of the following states: Wait For SIPI or

SENTER Sleep.

The reset value of this field is 0FFFH.

Only bit positions below N = CPUID.(EAX=0BH,

ECX=PKG_LVL):EBX[15:0] can be updated.

63:N

Reserved

606H

1542

MSR_RAPL_POWER_UNIT

Package

Unit Multipliers used in RAPL Interfaces (R/O)

3:0

Package

Power Units

See Section 14.9.1, “RAPL Interfaces.”

7:4

Package

Reserved

12:8

Package

Energy Status Units

Energy related information (in Joules) is based on the multiplier,

1/2^ESU; where ESU is an unsigned integer represented by bits

12:8. Default value is 0EH (or 61 micro-joules)

15:13

Package

Reserved

19:16

Package

Time Units

See Section 14.9.1, “RAPL Interfaces.”

63:20

Reserved

639H

1593

MSR_PP0_ENERGY_STATUS

Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

640H

1600

MSR_PP1_POWER_LIMIT

Package

PP1 RAPL Power Limit Control (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

641H

1601

MSR_PP1_ENERGY_STATUS

Package

PP1 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

642H

1602

MSR_PP1_POLICY

Package

PP1 Balance Policy (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

Table 35-28. MSRs Supported by 4th Generation Intel® Core™ Processors (Haswell microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec