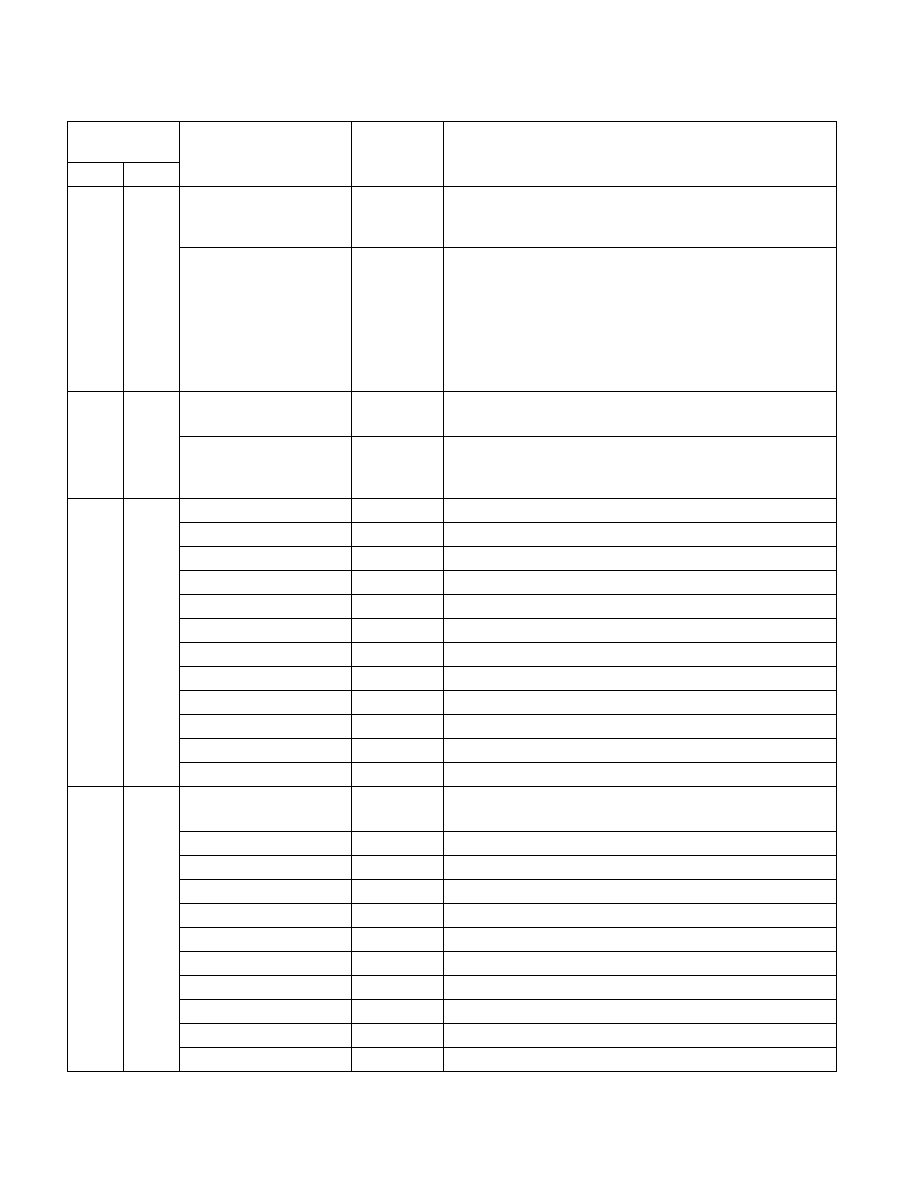

35-190 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

32

IN_TX: see Section 18.11.5.1

When IN_TX (bit 32) is set, AnyThread (bit 21) should be cleared to

prevent incorrect results

33

IN_TXCP: see Section 18.11.5.1

When IN_TXCP=1 & IN_TX=1 and in sampling, spurious PMI may

occur and transactions may continuously abort near overflow

conditions. Software should favor using IN_TXCP for counting over

sampling. If sampling, software should use large ŌĆ£sample-afterŌĆØ

value after clearing the counter configured to use IN_TXCP and

also always reset the counter even when no overflow condition

was reported.

189H

393

IA32_PERFEVTSEL3

THREAD

Performance Event Select for Counter 3 (R/W)

Supports all fields described inTable 35-2 and the fields below.

32

IN_TX: see Section 18.11.5.1

When IN_TX (bit 32) is set, AnyThread (bit 21) should be cleared to

prevent incorrect results

1C8H

456

MSR_LBR_SELECT

Thread

Last Branch Record Filtering Select Register (R/W)

0

CPL_EQ_0

1

CPL_NEQ_0

2

JCC

3

NEAR_REL_CALL

4

NEAR_IND_CALL

5

NEAR_RET

6

NEAR_IND_JMP

7

NEAR_REL_JMP

8

FAR_BRANCH

9

EN_CALL_STACK

63:9

Reserved.

1D9H

473

IA32_DEBUGCTL

Thread

Debug Control (R/W)

See Table 35-2.

0

LBR: Last Branch Record

1

BTF

5:2

Reserved.

6

TR: Branch Trace

7

BTS: Log Branch Trace Message to BTS buffer

8

BTINT

9

BTS_OFF_OS

10

BTS_OFF_USER

11

FREEZE_LBR_ON_PMI

12

FREEZE_PERFMON_ON_PMI

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec