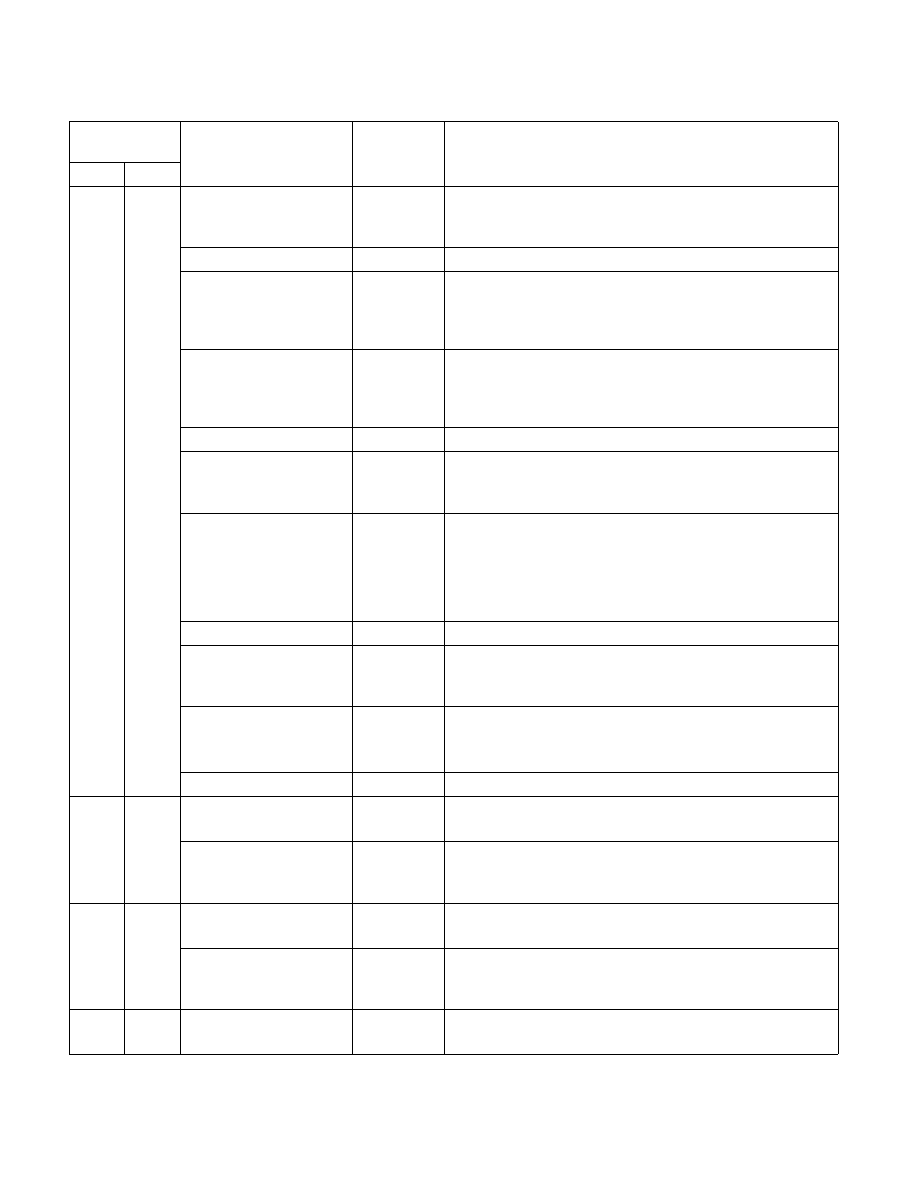

Vol. 3C 35-189

MODEL-SPECIFIC REGISTERS (MSRS)

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

27:16

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

When set to 1, indicates that Programmable Ratio Limits for Turbo

mode is enabled, and when set to 0, indicates Programmable Ratio

Limits for Turbo mode is disabled.

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

When set to 1, indicates that TDP Limits for Turbo mode are

programmable, and when set to 0, indicates TDP Limit for Turbo

mode is not programmable.

31:30

Reserved.

32

Package

Low Power Mode Support (LPM) (R/O)

When set to 1, indicates that LPM is supported, and when set to 0,

indicates LPM is not supported.

34:33

Package

Number of ConfigTDP Levels (R/O)

00: Only Base TDP level available.

01: One additional TDP level available.

02: Two additional TDP level available.

11: Reserved

39:35

Reserved.

47:40

Package

Maximum Efficiency Ratio (R/O)

The is the minimum ratio (maximum efficiency) that the processor

can operates, in units of 100MHz.

55:48

Package

Minimum Operating Ratio (R/O)

Contains the minimum supported

operating ratio in units of 100 MHz.

63:56

Reserved.

186H

390

IA32_PERFEVTSEL0

THREAD

Performance Event Select for Counter 0 (R/W)

Supports all fields described inTable 35-2 and the fields below.

32

IN_TX: see Section 18.11.5.1

When IN_TX (bit 32) is set, AnyThread (bit 21) should be cleared to

prevent incorrect results

187H

391

IA32_PERFEVTSEL1

THREAD

Performance Event Select for Counter 1 (R/W)

Supports all fields described inTable 35-2 and the fields below.

32

IN_TX: see Section 18.11.5.1

When IN_TX (bit 32) is set, AnyThread (bit 21) should be cleared to

prevent incorrect results

188H

392

IA32_PERFEVTSEL2

THREAD

Performance Event Select for Counter 2 (R/W)

Supports all fields described inTable 35-2 and the fields below.

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec