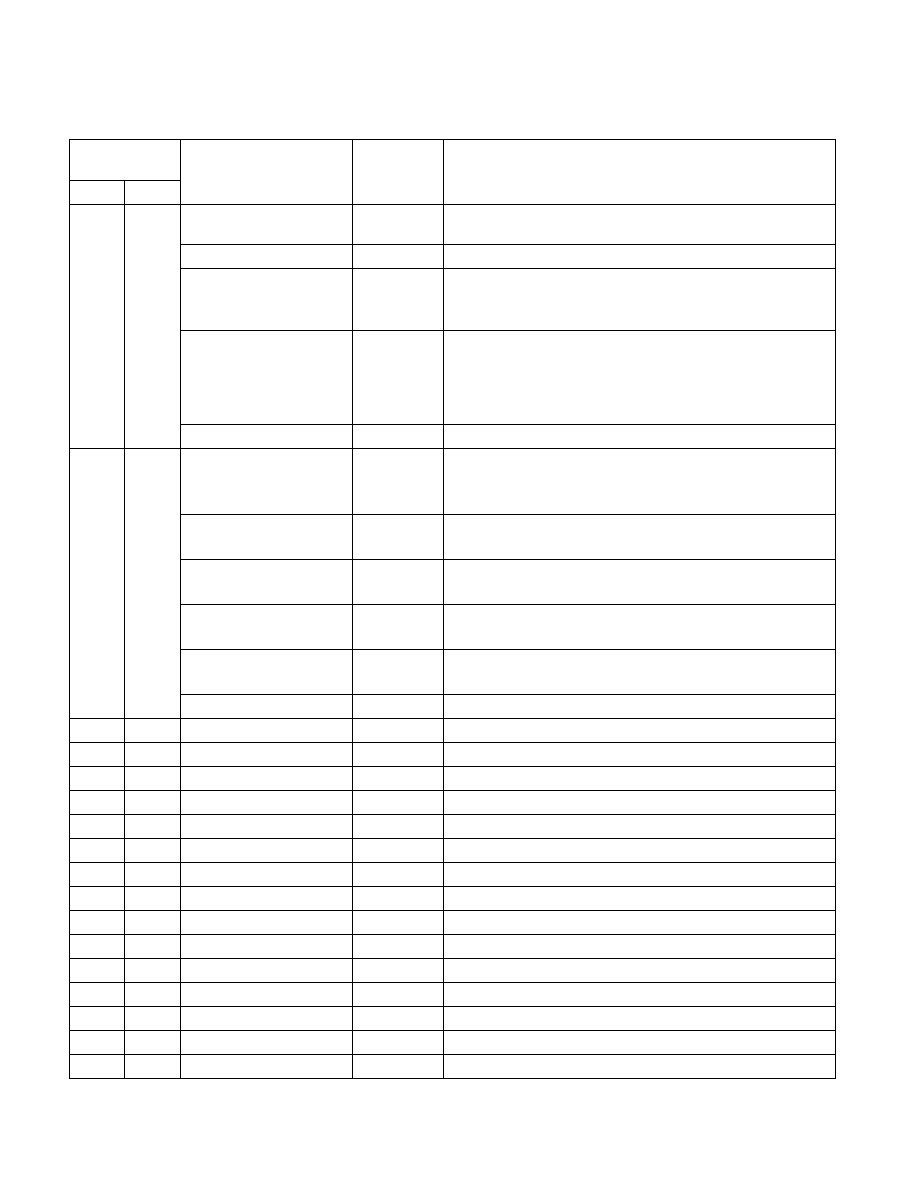

Vol. 3C 35-179

MODEL-SPECIFIC REGISTERS (MSRS)

1A2H

418

MSR_

TEMPERATURE_TARGET

Package

15:0

Reserved.

23:16

Temperature Target (RO)

The minimum temperature at which PROCHOT# will be asserted.

The value is degree C.

27:24

TCC Activation Offset (R/W)

Specifies a temperature offset in degrees C from the temperature

target (bits 23:16). PROCHOT# will assert at the offset target

temperature. Write is permitted only MSR_PLATFORM_INFO.[30] is

set.

63:28

Reserved.

1AEH

430

MSR_TURBO_RATIO_LIMIT

1

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 9C

Maximum turbo ratio limit of 9 core active.

15:8

Package

Maximum Ratio Limit for 10C

Maximum turbo ratio limit of 10core active.

23:16

Package

Maximum Ratio Limit for 11C

Maximum turbo ratio limit of 11 core active.

31:24

Package

Maximum Ratio Limit for 12C

Maximum turbo ratio limit of 12 core active.

63:32

Reserved

285H

645

IA32_MC5_CTL2

Package

286H

646

IA32_MC6_CTL2

Package

287H

647

IA32_MC7_CTL2

Package

288H

648

IA32_MC8_CTL2

Package

289H

649

IA32_MC9_CTL2

Package

28AH

650

IA32_MC10_CTL2

Package

See Table 35-2.

28BH

651

IA32_MC11_CTL2

Package

See Table 35-2.

28CH

652

IA32_MC12_CTL2

Package

See Table 35-2.

28DH

653

IA32_MC13_CTL2

Package

See Table 35-2.

28EH

654

IA32_MC14_CTL2

Package

See Table 35-2.

28FH

655

IA32_MC15_CTL2

Package

See Table 35-2.

290H

656

IA32_MC16_CTL2

Package

See Table 35-2.

291H

657

IA32_MC17_CTL2

Package

See Table 35-2.

292H

658

IA32_MC18_CTL2

Package

See Table 35-2.

293H

659

IA32_MC19_CTL2

Package

See Table 35-2.

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec