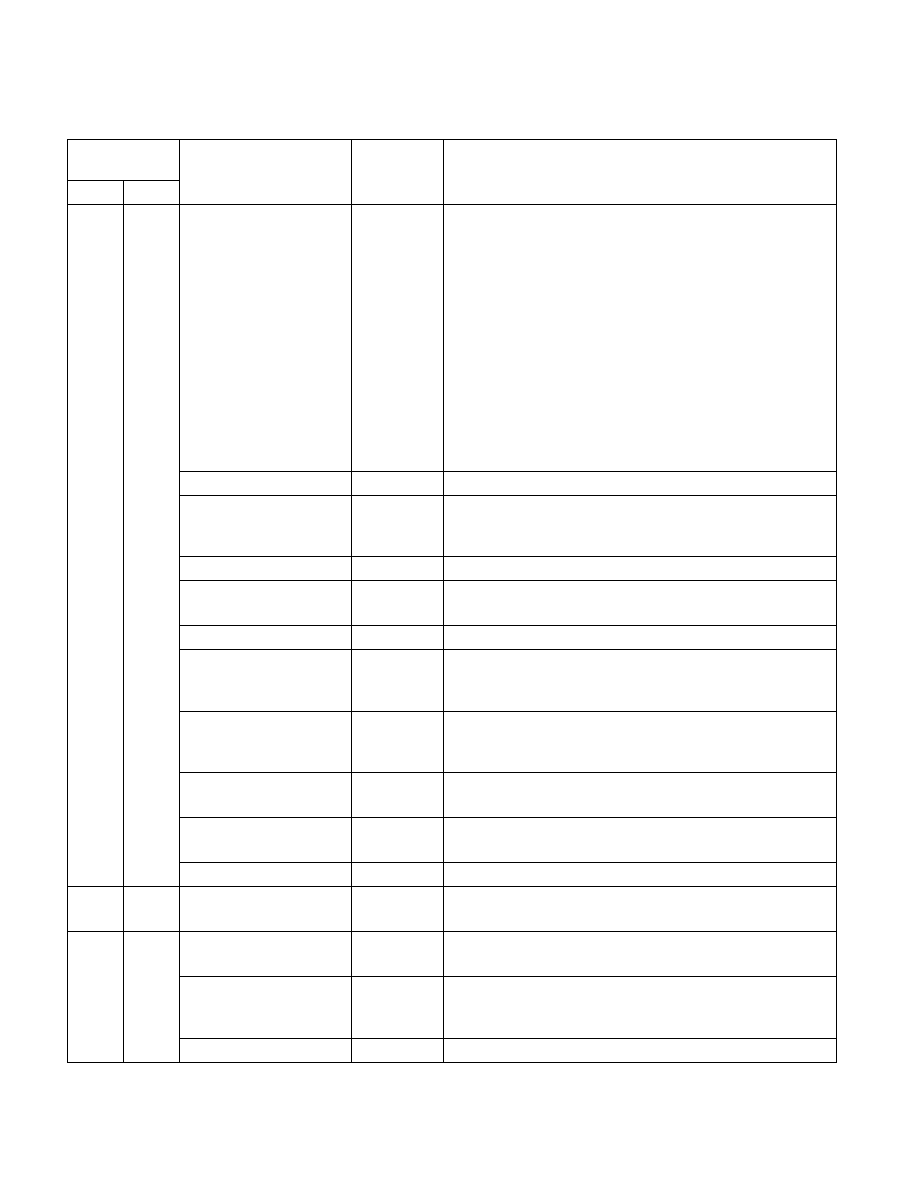

35-174 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

2:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power). for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

000b: C0/C1 (no package C-sate support)

001b: C2

010b: C6 no retention

011b: C6 retention

100b: C7

101b: C7s

111: No package C-state limit.

Note: This field cannot be used to limit package C-state to C3.

9:3

Reserved.

10

I/O MWAIT Redirection Enable (R/W)

When set, will map IO_read instructions sent to IO register specified

by MSR_PMG_IO_CAPTURE_BASE to MWAIT instructions

14:11

Reserved.

15

CFG Lock (R/WO)

When set, lock bits 15:0 of this register until next reset.

24:16

Reserved.

25

C3 state auto demotion enable (R/W)

When set, the processor will conditionally demote C6/C7 requests

to C3 based on uncore auto-demote information.

26

C1 state auto demotion enable (R/W)

When set, the processor will conditionally demote C3/C6/C7

requests to C1 based on uncore auto-demote information.

27

Enable C3 undemotion (R/W)

When set, enables undemotion from demoted C3.

28

Enable C1 undemotion (R/W)

When set, enables undemotion from demoted C1.

63:29

Reserved.

639H

1593

MSR_PP0_ENERGY_STATUS Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

648H

1608

MSR_CONFIG_TDP_

NOMINAL

Package

Base TDP Ratio (R/O)

7:0

Config_TDP_Base

Base TDP level ratio to be used for this specific processor (in units

of 100 MHz).

63:8

Reserved.

Table 35-23. Additional MSRs Supported by 3rd Generation Intel® Core™ Processors (based on Intel®

microarchitecture code name Ivy Bridge) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec