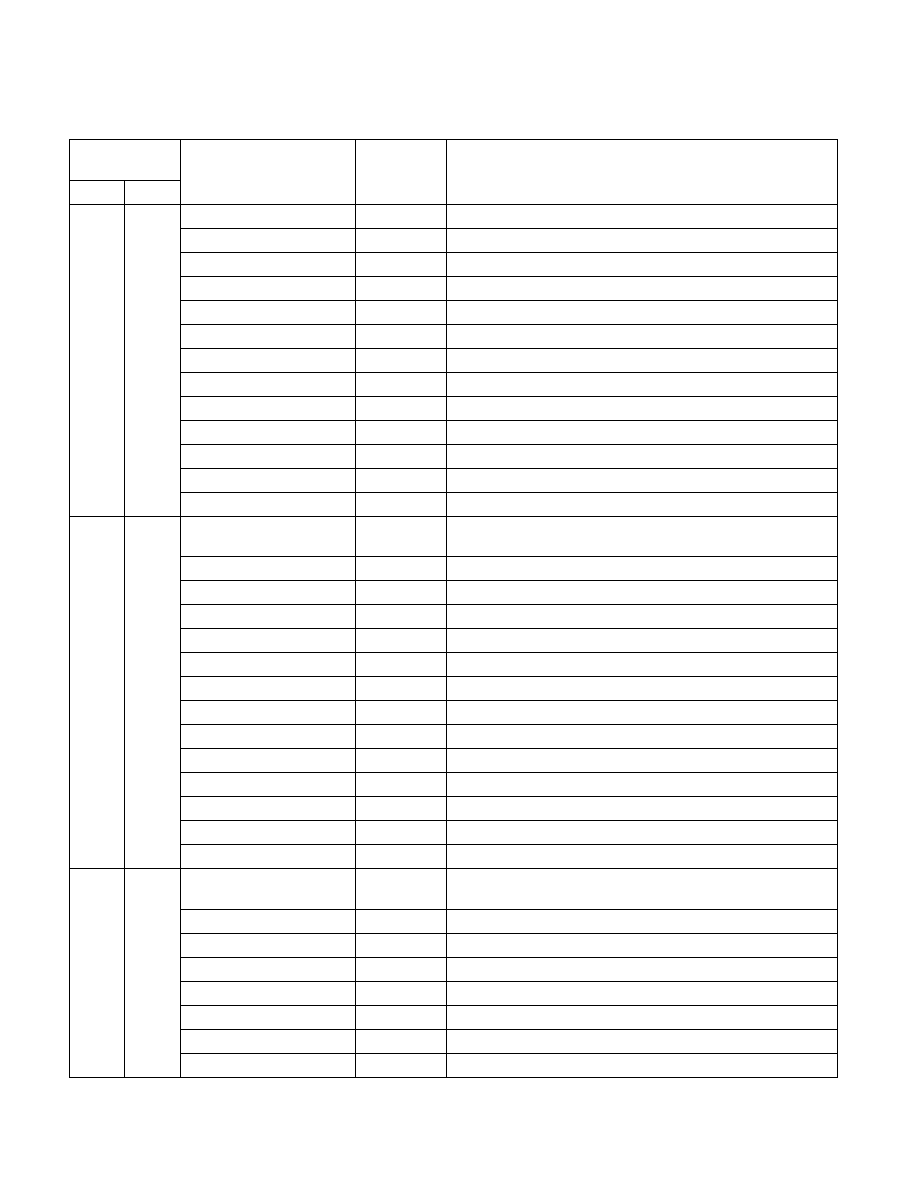

Vol. 3C 35-153

MODEL-SPECIFIC REGISTERS (MSRS)

3

Thread

Ovf_PMC3

4

Core

Ovf_PMC4 (if CPUID.0AH:EAX[15:8] > 4)

5

Core

Ovf_PMC5 (if CPUID.0AH:EAX[15:8] > 5)

6

Core

Ovf_PMC6 (if CPUID.0AH:EAX[15:8] > 6)

7

Core

Ovf_PMC7 (if CPUID.0AH:EAX[15:8] > 7)

31:8

Reserved.

32

Thread

Ovf_FixedCtr0

33

Thread

Ovf_FixedCtr1

34

Thread

Ovf_FixedCtr2

60:35

Reserved.

61

Thread

Ovf_Uncore

62

Thread

Ovf_BufDSSAVE

63

Thread

CondChgd

38FH

911

IA32_PERF_GLOBAL_CTRL

Thread

See Table 35-2. See Section 18.4.2, “Global Counter Control

0

Thread

Set 1 to enable PMC0 to count

1

Thread

Set 1 to enable PMC1 to count

2

Thread

Set 1 to enable PMC2 to count

3

Thread

Set 1 to enable PMC3 to count

4

Core

Set 1 to enable PMC4 to count (if CPUID.0AH:EAX[15:8] > 4)

5

Core

Set 1 to enable PMC5 to count (if CPUID.0AH:EAX[15:8] > 5)

6

Core

Set 1 to enable PMC6 to count (if CPUID.0AH:EAX[15:8] > 6)

7

Core

Set 1 to enable PMC7 to count (if CPUID.0AH:EAX[15:8] > 7)

31:8

Reserved.

32

Thread

Set 1 to enable FixedCtr0 to count

33

Thread

Set 1 to enable FixedCtr1 to count

34

Thread

Set 1 to enable FixedCtr2 to count

63:35

Reserved.

390H

912

IA32_PERF_GLOBAL_OVF_

CTRL

See Table 35-2. See Section 18.4.2, “Global Counter Control

0

Thread

Set 1 to clear Ovf_PMC0

1

Thread

Set 1 to clear Ovf_PMC1

2

Thread

Set 1 to clear Ovf_PMC2

3

Thread

Set 1 to clear Ovf_PMC3

4

Core

Set 1 to clear Ovf_PMC4 (if CPUID.0AH:EAX[15:8] > 4)

5

Core

Set 1 to clear Ovf_PMC5 (if CPUID.0AH:EAX[15:8] > 5)

6

Core

Set 1 to clear Ovf_PMC6 (if CPUID.0AH:EAX[15:8] > 6)

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec