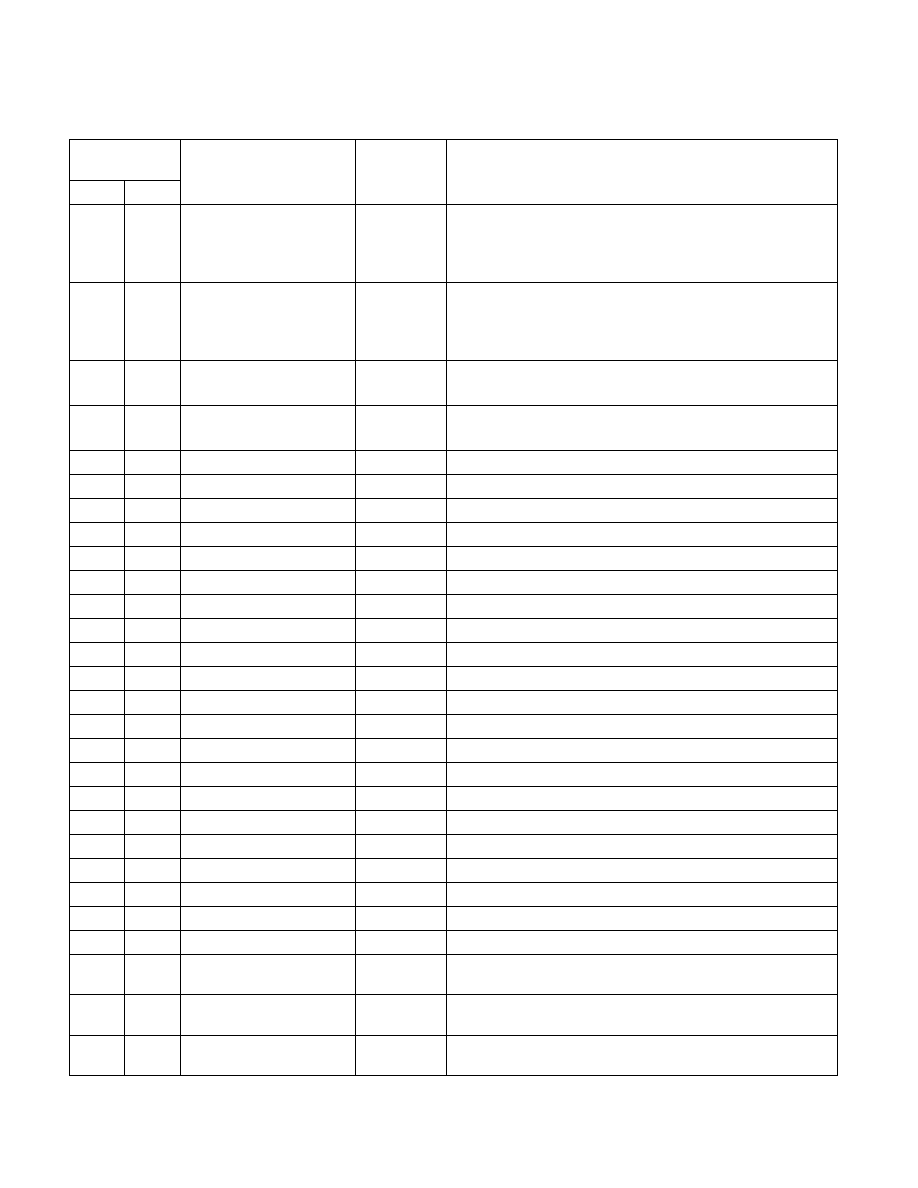

Vol. 3C 35-151

MODEL-SPECIFIC REGISTERS (MSRS)

1DDH

477

MSR_LER_FROM_LIP Thread

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

1DEH

478

MSR_LER_TO_LIP

Thread

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch

instruction that the processor executed prior to the last exception

that was generated or the last interrupt that was handled.

1F2H

498

IA32_SMRR_PHYSBASE

Core

See Table 35-2.

1F3H

499

IA32_SMRR_PHYSMASK

Core

See Table 35-2.

1FCH

508

MSR_POWER_CTL Core

See

http://biosbits.org.

200H

512

IA32_MTRR_PHYSBASE0

Thread

See Table 35-2.

201H

513

IA32_MTRR_PHYSMASK0

Thread

See Table 35-2.

202H

514

IA32_MTRR_PHYSBASE1

Thread

See Table 35-2.

203H

515

IA32_MTRR_PHYSMASK1

Thread

See Table 35-2.

204H

516

IA32_MTRR_PHYSBASE2

Thread

See Table 35-2.

205H

517

IA32_MTRR_PHYSMASK2

Thread

See Table 35-2.

206H

518

IA32_MTRR_PHYSBASE3

Thread

See Table 35-2.

207H

519

IA32_MTRR_PHYSMASK3

Thread

See Table 35-2.

208H

520

IA32_MTRR_PHYSBASE4

Thread

See Table 35-2.

209H

521

IA32_MTRR_PHYSMASK4

Thread

See Table 35-2.

20AH

522

IA32_MTRR_PHYSBASE5

Thread

See Table 35-2.

20BH

523

IA32_MTRR_PHYSMASK5

Thread

20CH

524

IA32_MTRR_PHYSBASE6

Thread

20DH

525

IA32_MTRR_PHYSMASK6

Thread

20EH

526

IA32_MTRR_PHYSBASE7

Thread

20FH

527

IA32_MTRR_PHYSMASK7

Thread

210H

528

IA32_MTRR_PHYSBASE8

Thread

See Table 35-2.

211H

529

IA32_MTRR_PHYSMASK8

Thread

See Table 35-2.

212H

530

IA32_MTRR_PHYSBASE9

Thread

See Table 35-2.

213H

531

IA32_MTRR_PHYSMASK9

Thread

See Table 35-2.

250H

592

IA32_MTRR_FIX64K_

00000

Thread

258H

600

IA32_MTRR_FIX16K_

80000

Thread

259H

601

IA32_MTRR_FIX16K_

A0000

Thread

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec