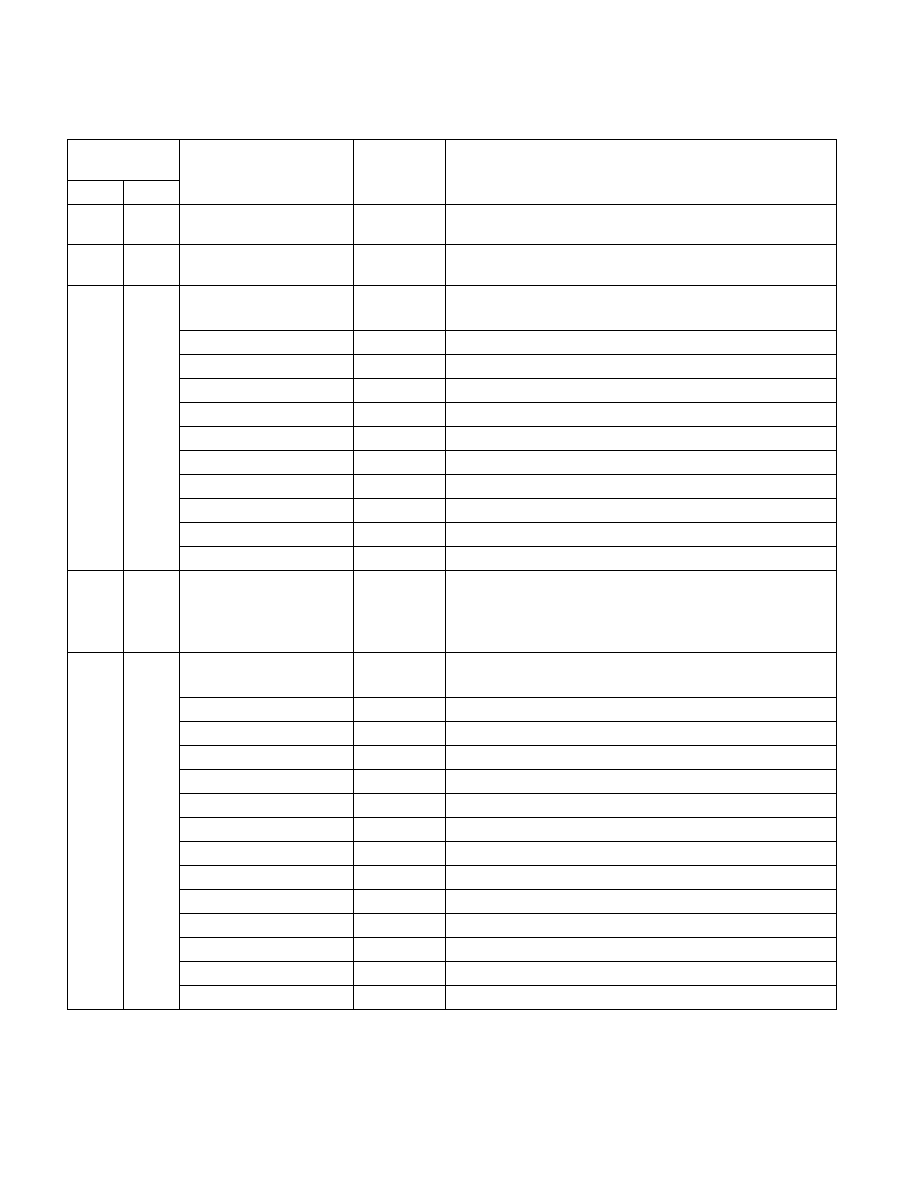

35-150 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

1B1H

433

IA32_PACKAGE_THERM_

STATUS

Package

See Table 35-2.

1B2H

434

IA32_PACKAGE_THERM_

INTERRUPT

Package

See Table 35-2.

1C8H

456

MSR_LBR_SELECT

Thread

Last Branch Record Filtering Select Register (R/W)

See Section 17.7.2, “Filtering of Last Branch Records.”

0

CPL_EQ_0

1

CPL_NEQ_0

2

JCC

3

NEAR_REL_CALL

4

NEAR_IND_CALL

5

NEAR_RET

6

NEAR_IND_JMP

7

NEAR_REL_JMP

8

FAR_BRANCH

63:9

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Thread

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-3) that points to the MSR containing the

most recent branch record.

See MSR_LASTBRANCH_0_FROM_IP (at 680H).

1D9H

473

IA32_DEBUGCTL

Thread

Debug Control (R/W)

See Table 35-2.

0

LBR: Last Branch Record

1

BTF

5:2

Reserved.

6

TR: Branch Trace

7

BTS: Log Branch Trace Message to BTS buffer

8

BTINT

9

BTS_OFF_OS

10

BTS_OFF_USER

11

FREEZE_LBR_ON_PMI

12

FREEZE_PERFMON_ON_PMI

13

ENABLE_UNCORE_PMI

14

FREEZE_WHILE_SMM

63:15

Reserved.

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec