Vol. 3C 35-147

MODEL-SPECIFIC REGISTERS (MSRS)

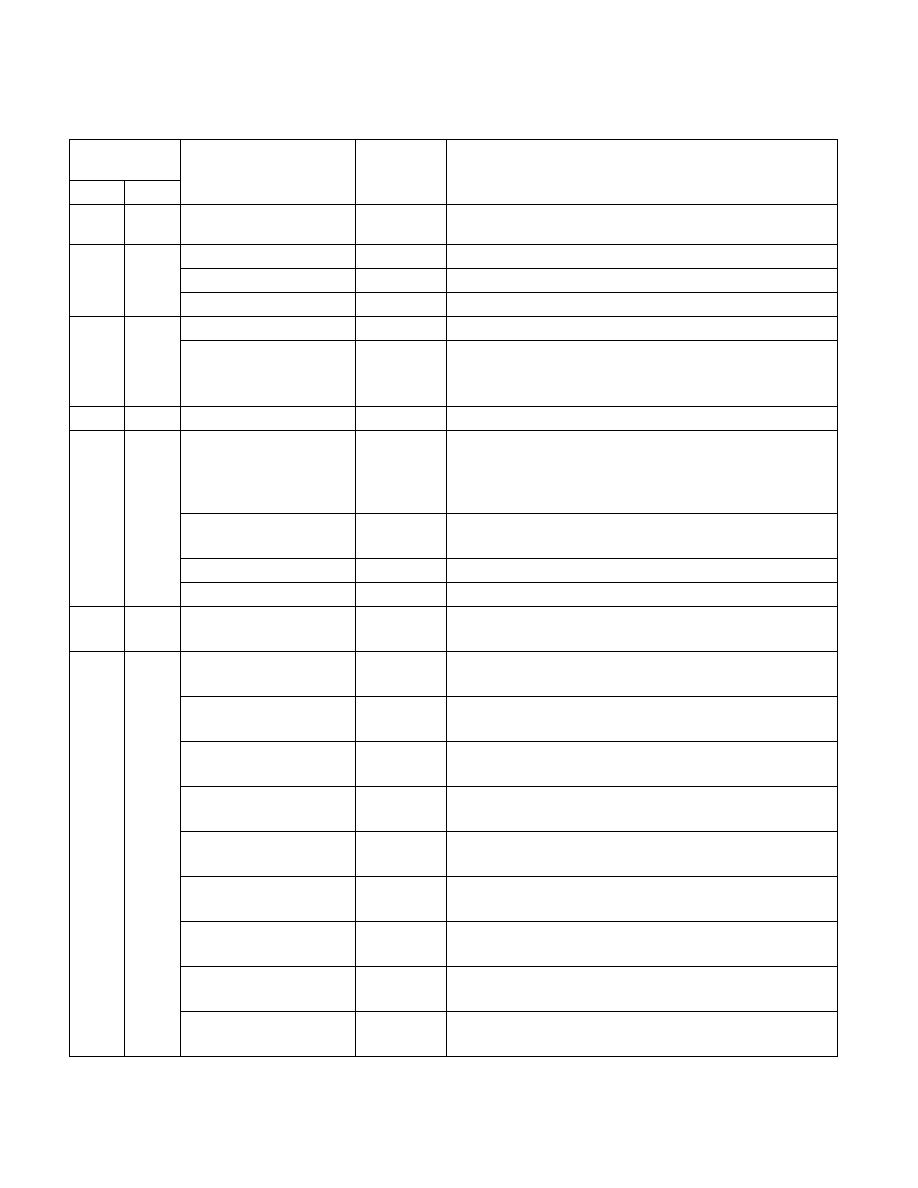

18DH

397

IA32_

PERFEVTSEL7

Core

See Table 35-2; If CPUID.0AH:EAX[15:8] = 8

198H

408

IA32_PERF_STATUS

Package

See Table 35-2.

15:0

Current Performance State Value.

63:16

Reserved.

198H

408

MSR_PERF_STATUS

Package

47:32

Core Voltage (R/O)

P-state core voltage can be computed by

MSR_PERF_STATUS[37:32] * (float) 1/(2^13).

199H

409

IA32_PERF_CTL

Thread

See Table 35-2.

19AH

410

IA32_CLOCK_

MODULATION

Thread

Clock Modulation (R/W)

See Table 35-2

IA32_CLOCK_MODULATION MSR was originally named

IA32_THERM_CONTROL MSR.

3:0

On demand Clock Modulation Duty Cycle (R/W)

In 6.25% increment

4

On demand Clock Modulation Enable (R/W)

63:5

Reserved.

19BH

411

IA32_THERM_INTERRUPT

Core

Thermal Interrupt Control (R/W)

See Table 35-2.

19CH

412

IA32_THERM_STATUS

Core

Thermal Monitor Status (R/W)

See Table 35-2.

0

Thermal status (RO)

See Table 35-2.

1

Thermal status log (R/WC0)

See Table 35-2.

2

PROTCHOT # or FORCEPR# status (RO)

See Table 35-2.

3

PROTCHOT # or FORCEPR# log (R/WC0)

See Table 35-2.

4

Critical Temperature status (RO)

See Table 35-2.

5

Critical Temperature status log (R/WC0)

See Table 35-2.

6

Thermal threshold #1 status (RO)

See Table 35-2.

7

Thermal threshold #1 log (R/WC0)

See Table 35-2.

Table 35-18. MSRs Supported by Intel® Processors

based on Intel® microarchitecture code name Sandy Bridge (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec