35-142 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.9

MSRS IN INTEL

®

PROCESSOR FAMILY BASED ON INTEL

®

MICROARCHITECTURE CODE NAME SANDY BRIDGE

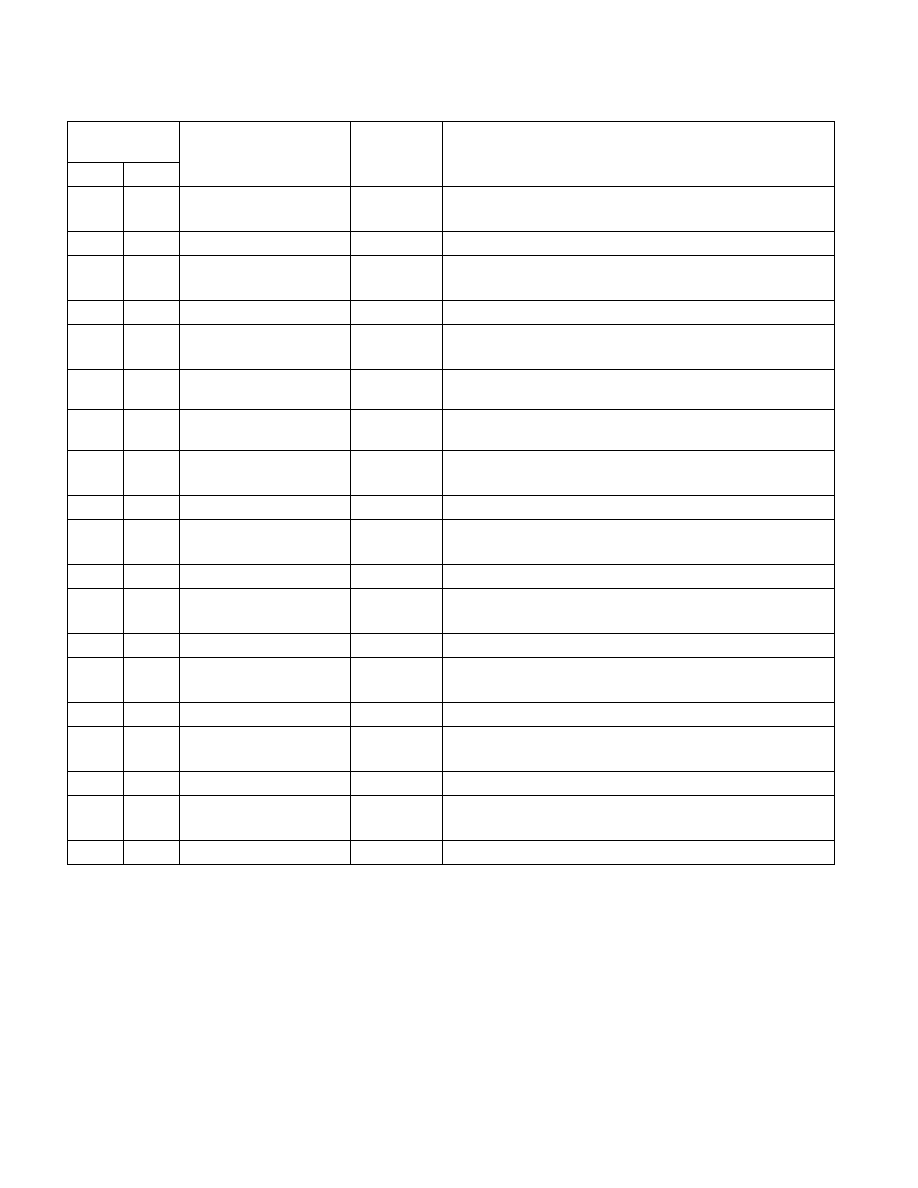

Table 35-18 lists model-specific registers (MSRs) that are common to Intel

®

processor family based on Intel micro-

architecture code name Sandy Bridge. These processors have a CPUID signature with DisplayFamily_DisplayModel

of 06_2AH, 06_2DH, see Table 35-1. Additional MSRs specific to 06_2AH are listed in Table 35-19.

F58H

3928

MSR_C8_PMON_EVNT_

SEL4

Package

Uncore C-box 8 perfmon event select MSR.

F59H

3929

MSR_C8_PMON_CTR4

Package

Uncore C-box 8 perfmon counter MSR.

F5AH

3930

MSR_C8_PMON_EVNT_

SEL5

Package

Uncore C-box 8 perfmon event select MSR.

F5BH

3931

MSR_C8_PMON_CTR5

Package

Uncore C-box 8 perfmon counter MSR.

FC0H

4032

MSR_C9_PMON_BOX_CTRL Package

Uncore C-box 9 perfmon local box control MSR.

FC1H

4033

MSR_C9_PMON_BOX_

STATUS

Package

Uncore C-box 9 perfmon local box status MSR.

FC2H

4034

MSR_C9_PMON_BOX_OVF_

CTRL

Package

Uncore C-box 9 perfmon local box overflow control MSR.

FD0H

4048

MSR_C9_PMON_EVNT_

SEL0

Package

Uncore C-box 9 perfmon event select MSR.

FD1H

4049

MSR_C9_PMON_CTR0

Package

Uncore C-box 9 perfmon counter MSR.

FD2H

4050

MSR_C9_PMON_EVNT_

SEL1

Package

Uncore C-box 9 perfmon event select MSR.

FD3H

4051

MSR_C9_PMON_CTR1

Package

Uncore C-box 9 perfmon counter MSR.

FD4H

4052

MSR_C9_PMON_EVNT_

SEL2

Package

Uncore C-box 9 perfmon event select MSR.

FD5H

4053

MSR_C9_PMON_CTR2

Package

Uncore C-box 9 perfmon counter MSR.

FD6H

4054

MSR_C9_PMON_EVNT_

SEL3

Package

Uncore C-box 9 perfmon event select MSR.

FD7H

4055

MSR_C9_PMON_CTR3

Package

Uncore C-box 9 perfmon counter MSR.

FD8H

4056

MSR_C9_PMON_EVNT_

SEL4

Package

Uncore C-box 9 perfmon event select MSR.

FD9H

4057

MSR_C9_PMON_CTR4

Package

Uncore C-box 9 perfmon counter MSR.

FDAH

4058

MSR_C9_PMON_EVNT_

SEL5

Package

Uncore C-box 9 perfmon event select MSR.

FDBH

4059

MSR_C9_PMON_CTR5

Package

Uncore C-box 9 perfmon counter MSR.

Table 35-17. Additional MSRs Supported by Intel® Xeon® Processor E7 Family (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec