Vol. 3C 35-125

MODEL-SPECIFIC REGISTERS (MSRS)

35.6.2 Additional MSRs in the Intel

┬о

Xeon

┬о

Processor 7500 Series

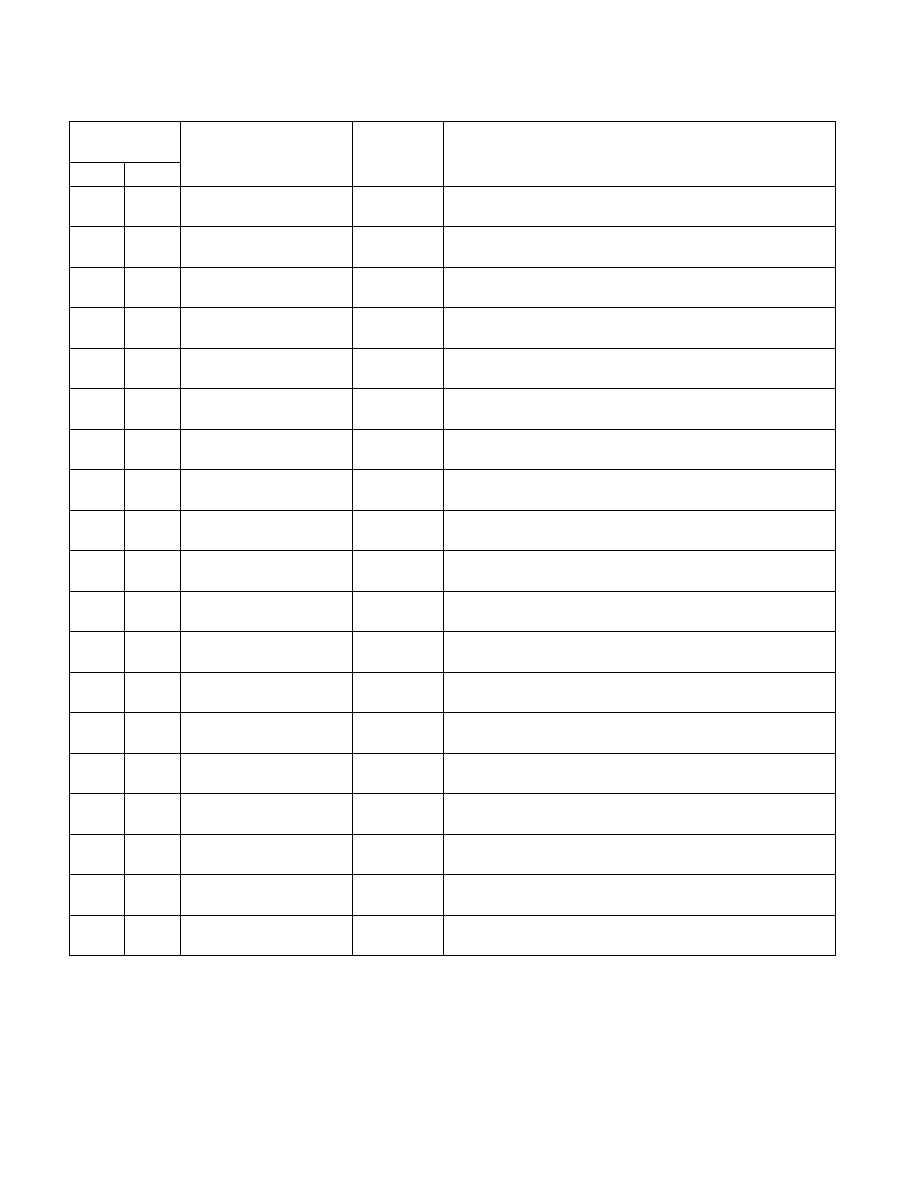

Intel Xeon Processor 7500 series support MSRs listed in Table 35-13 (except MSR address 1ADH) and additional

model-specific registers listed in Table 35-15. These processors have a CPUID signature with

DisplayFamily_DisplayModel of 06_2EH.

394H

916

MSR_UNCORE_FIXED_CTR0 Package

See Section 18.7.2.1, тАЬUncore Performance Monitoring

395H

917

MSR_UNCORE_FIXED_CTR_

CTRL

Package

See Section 18.7.2.1, тАЬUncore Performance Monitoring

396H

918

MSR_UNCORE_ADDR_

OPCODE_MATCH

Package

See Section 18.7.2.3, тАЬUncore Address/Opcode Match MSR.тАЭ

3B0H

960

MSR_UNCORE_PMC0

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B1H

961

MSR_UNCORE_PMC1

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B2H

962

MSR_UNCORE_PMC2

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B3H

963

MSR_UNCORE_PMC3

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B4H

964

MSR_UNCORE_PMC4

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B5H

965

MSR_UNCORE_PMC5

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B6H

966

MSR_UNCORE_PMC6

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3B7H

967

MSR_UNCORE_PMC7

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C0H

944

MSR_UNCORE_

PERFEVTSEL0

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C1H

945

MSR_UNCORE_

PERFEVTSEL1

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C2H

946

MSR_UNCORE_

PERFEVTSEL2

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C3H

947

MSR_UNCORE_

PERFEVTSEL3

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C4H

948

MSR_UNCORE_

PERFEVTSEL4

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C5H

949

MSR_UNCORE_

PERFEVTSEL5

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C6H

950

MSR_UNCORE_

PERFEVTSEL6

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

3C7H

951

MSR_UNCORE_

PERFEVTSEL7

Package

See Section 18.7.2.2, тАЬUncore Performance Event Configuration

Table 35-14. Additional MSRs in Intel┬о Xeon┬о Processor 5500 and 3400 Series (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec