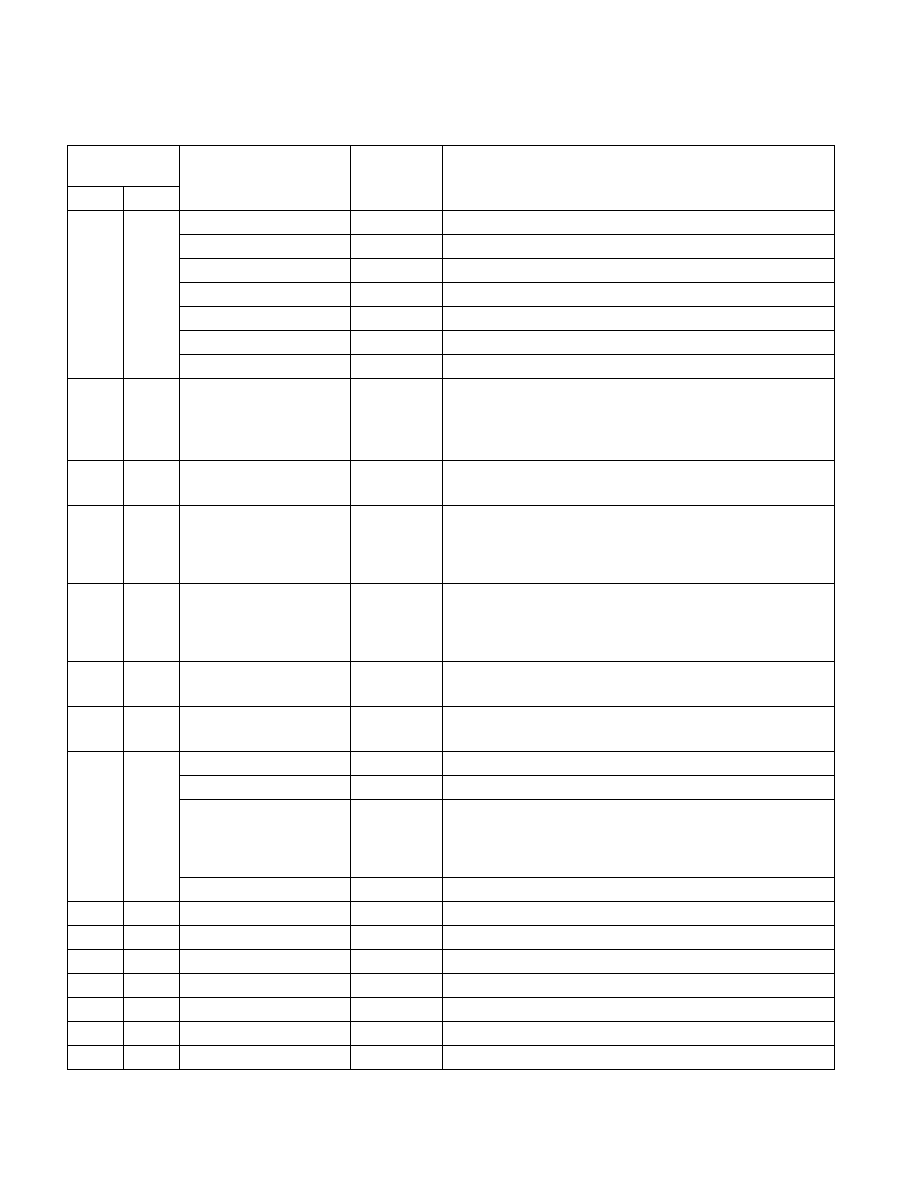

35-114 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

3

NEAR_REL_CALL

4

NEAR_IND_CALL

5

NEAR_RET

6

NEAR_IND_JMP

7

NEAR_REL_JMP

8

FAR_BRANCH

63:9

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Thread

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-3) that points to the MSR containing the

most recent branch record.

See MSR_LASTBRANCH_0_FROM_IP (at 680H).

1D9H

473

IA32_DEBUGCTL

Thread

Debug Control (R/W)

See Table 35-2.

1DDH

477

MSR_LER_FROM_LIP Thread

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

1DEH

478

MSR_LER_TO_LIP

Thread

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch

instruction that the processor executed prior to the last exception

that was generated or the last interrupt that was handled.

1F2H

498

IA32_SMRR_PHYSBASE

Core

See Table 35-2.

1F3H

499

IA32_SMRR_PHYSMASK

Core

See Table 35-2.

1FCH

508

MSR_POWER_CTL

Core

Power Control Register. See http://biosbits.org.

0

Reserved.

1

Package

C1E Enable (R/W)

When set to ‘1’, will enable the CPU to switch to the Minimum

Enhanced Intel SpeedStep Technology operating point when all

execution cores enter MWAIT (C1).

63:2

Reserved.

200H

512

IA32_MTRR_PHYSBASE0

Thread

See Table 35-2.

201H

513

IA32_MTRR_PHYSMASK0

Thread

See Table 35-2.

202H

514

IA32_MTRR_PHYSBASE1

Thread

See Table 35-2.

203H

515

IA32_MTRR_PHYSMASK1

Thread

See Table 35-2.

204H

516

IA32_MTRR_PHYSBASE2

Thread

See Table 35-2.

205H

517

IA32_MTRR_PHYSMASK2

Thread

See Table 35-2.

206H

518

IA32_MTRR_PHYSBASE3

Thread

See Table 35-2.

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec