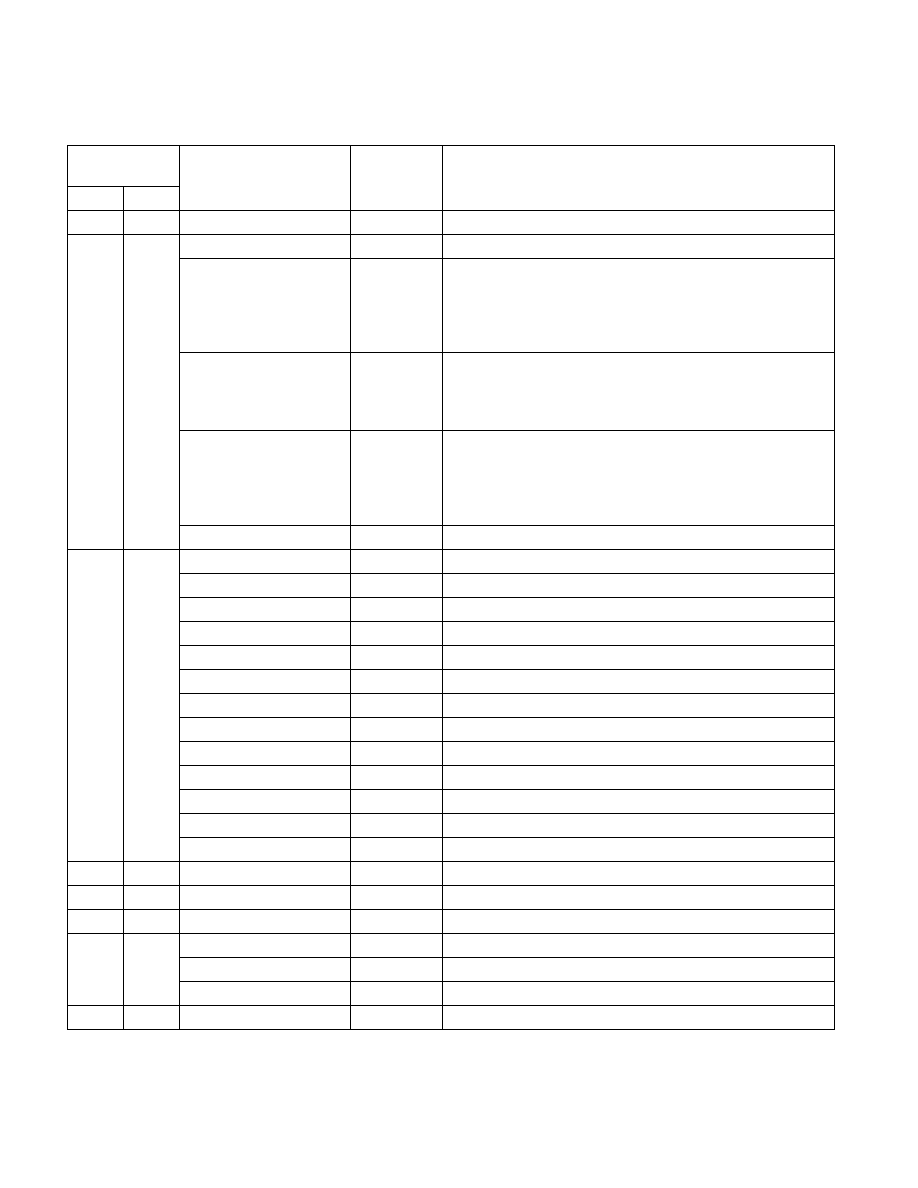

35-110 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

179H

377

IA32_MCG_CAP

Thread

See Table 35-2.

17AH

378

IA32_MCG_STATUS

Thread

0

RIPV

When set, bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check

was generated) can be used to restart the program. If cleared, the

program cannot be reliably restarted.

1

EIPV

When set, bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check

was generated) is directly associated with the error.

2

MCIP

When set, bit indicates that a machine check has been generated. If

a second machine check is detected while this bit is still set, the

processor enters a shutdown state. Software should write this bit

to 0 after processing a machine check exception.

63:3

Reserved.

186H

390

IA32_PERFEVTSEL0

Thread

See Table 35-2.

7:0

Event Select

15:8

UMask

16

USR

17

OS

18

Edge

19

PC

20

INT

21

AnyThread

22

EN

23

INV

31:24

CMASK

63:32

Reserved.

187H

391

IA32_PERFEVTSEL1

Thread

See Table 35-2.

188H

392

IA32_PERFEVTSEL2

Thread

See Table 35-2.

189H

393

IA32_PERFEVTSEL3

Thread

See Table 35-2.

198H

408

IA32_PERF_STATUS

Core

See Table 35-2.

15:0

Current Performance State Value.

63:16

Reserved.

199H

409

IA32_PERF_CTL

Thread

See Table 35-2.

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec