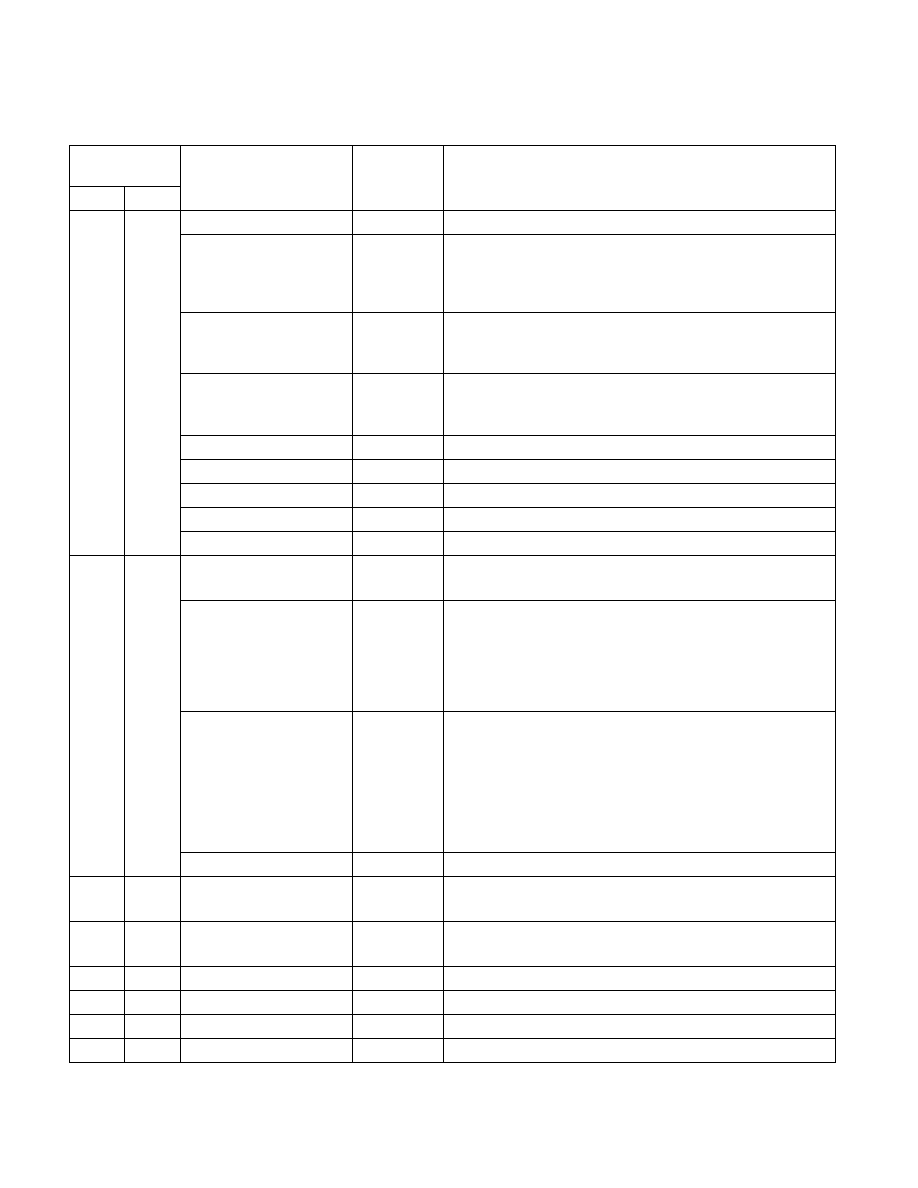

Vol. 3C 35-109

MODEL-SPECIFIC REGISTERS (MSRS)

23:16

Reserved.

24

Interrupt filtering enable (R/W)

When set, processor cores in a deep C-State will wake only when

the event message is destined for that core. When 0, all processor

cores in a deep C-State will wake for an event message.

25

C3 state auto demotion enable (R/W)

When set, the processor will conditionally demote C6/C7 requests

to C3 based on uncore auto-demote information.

26

C1 state auto demotion enable (R/W)

When set, the processor will conditionally demote C3/C6/C7

requests to C1 based on uncore auto-demote information.

27

Enable C3 Undemotion (R/W)

28

Enable C1 Undemotion (R/W)

29

Package C State Demotion Enable (R/W)

30

Package C State UnDemotion Enable (R/W)

63:31

Reserved.

E4H

228

MSR_PMG_IO_CAPTURE_

BASE

Core

Power Management IO Redirection in C-state (R/W)

See http://biosbits.org.

15:0

LVL_2 Base Address (R/W)

Specifies the base address visible to software for IO redirection. If

IO MWAIT Redirection is enabled, reads to this address will be

consumed by the power management logic and decoded to MWAIT

instructions. When IO port address redirection is enabled, this is the

IO port address reported to the OS/software.

18:16

C-state Range (R/W)

Specifies the encoding value of the maximum C-State code name to

be included when IO read to MWAIT redirection is enabled by

MSR_PKG_CST_CONFIG_CONTROL[bit10]:

000b - C3 is the max C-State to include

001b - C6 is the max C-State to include

010b - C7 is the max C-State to include

63:19

Reserved.

E7H

231

IA32_MPERF

Thread

Maximum Performance Frequency Clock Count (RW)

See Table 35-2.

E8H

232

IA32_APERF

Thread

Actual Performance Frequency Clock Count (RW)

See Table 35-2.

FEH

254

IA32_MTRRCAP

Thread

174H

372

IA32_SYSENTER_CS

Thread

175H

373

IA32_SYSENTER_ESP

Thread

See Table 35-2.

176H

374

IA32_SYSENTER_EIP

Thread

See Table 35-2.

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec