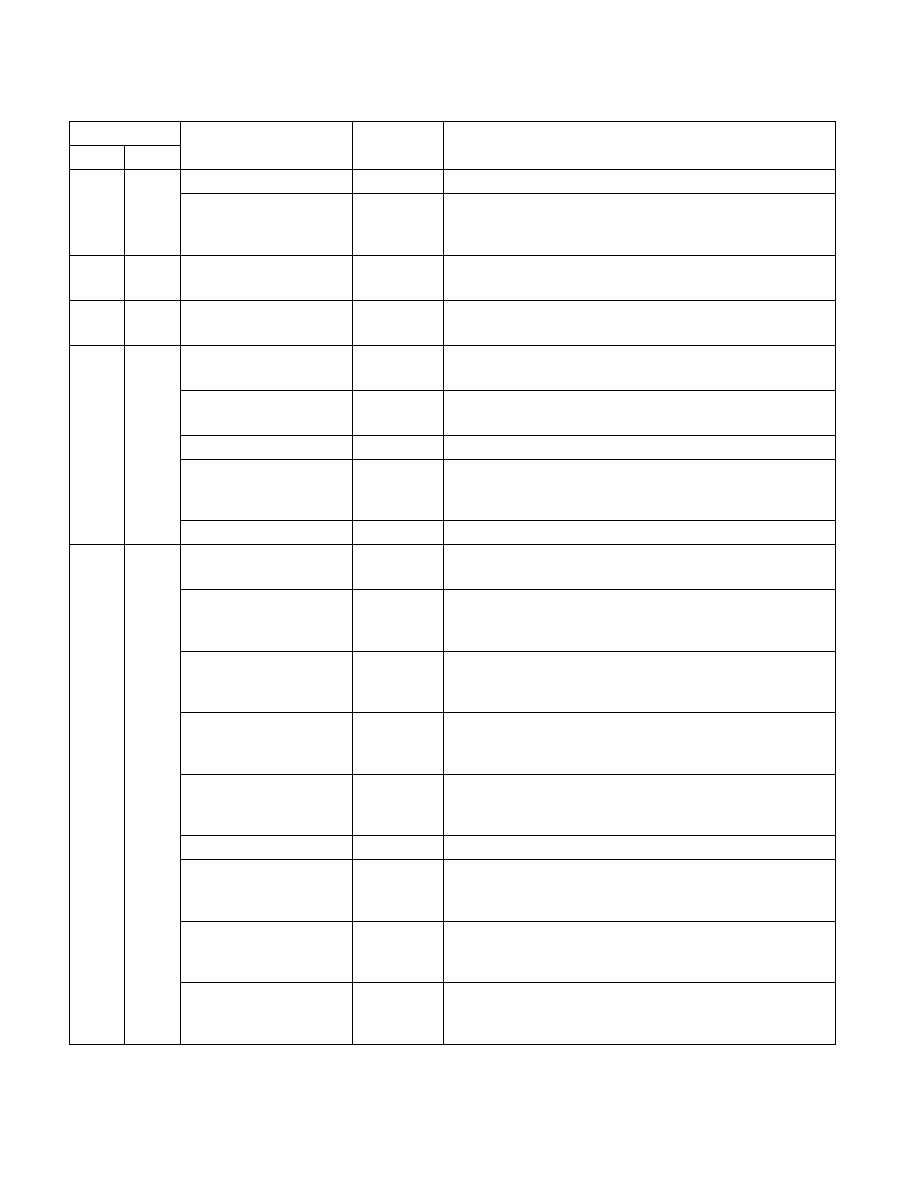

Vol. 3C 35-99

MODEL-SPECIFIC REGISTERS (MSRS)

632H

1586

MSR_PKG_C10_RESIDENCY Package

Note: C-state values are processor specific C-state code names,

63:0

Package C10 Residency Counter. (R/O)

Value since last reset that the entire SOC is in an S0i3 state. Count

at the same frequency as the TSC.

639H

1593

MSR_PP0_ENERGY_STATU

S

Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

641H

1601

MSR_PP1_ENERGY_STATU

S

Package

PP1 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

64CH

1612

MSR_TURBO_ACTIVATION_

RATIO

Package

ConfigTDP Control (R/W)

7:0

MAX_NON_TURBO_RATIO (RW/L)

System BIOS can program this field.

30:8

Reserved.

31

TURBO_ACTIVATION_RATIO_Lock (RW/L)

When this bit is set, the content of this register is locked until a

reset.

63:32

Reserved.

64FH

1615

MSR_CORE_PERF_LIMIT_RE

ASONS

Package

Indicator of Frequency Clipping in Processor Cores (R/W)

(frequency refers to processor core frequency)

0

PROCHOT Status (R0)

When set, processor core frequency is reduced below the

operating system request due to assertion of external PROCHOT.

1

Thermal Status (R0)

When set, frequency is reduced below the operating system

request due to a thermal event.

2

Package-Level Power Limiting PL1 Status (R0)

When set, frequency is reduced below the operating system

request due to package-level power limiting PL1.

3

Package-Level PL2 Power Limiting Status (R0)

When set, frequency is reduced below the operating system

request due to package-level power limiting PL2.

8:4

Reserved.

9

Core Power Limiting Status (R0)

When set, frequency is reduced below the operating system

request due to domain-level power limiting.

10

VR Therm Alert Status (R0)

When set, frequency is reduced below the operating system

request due to a thermal alert from the Voltage Regulator.

11

Max Turbo Limit Status (R0)

When set, frequency is reduced below the operating system

request due to multi-core turbo limits.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec