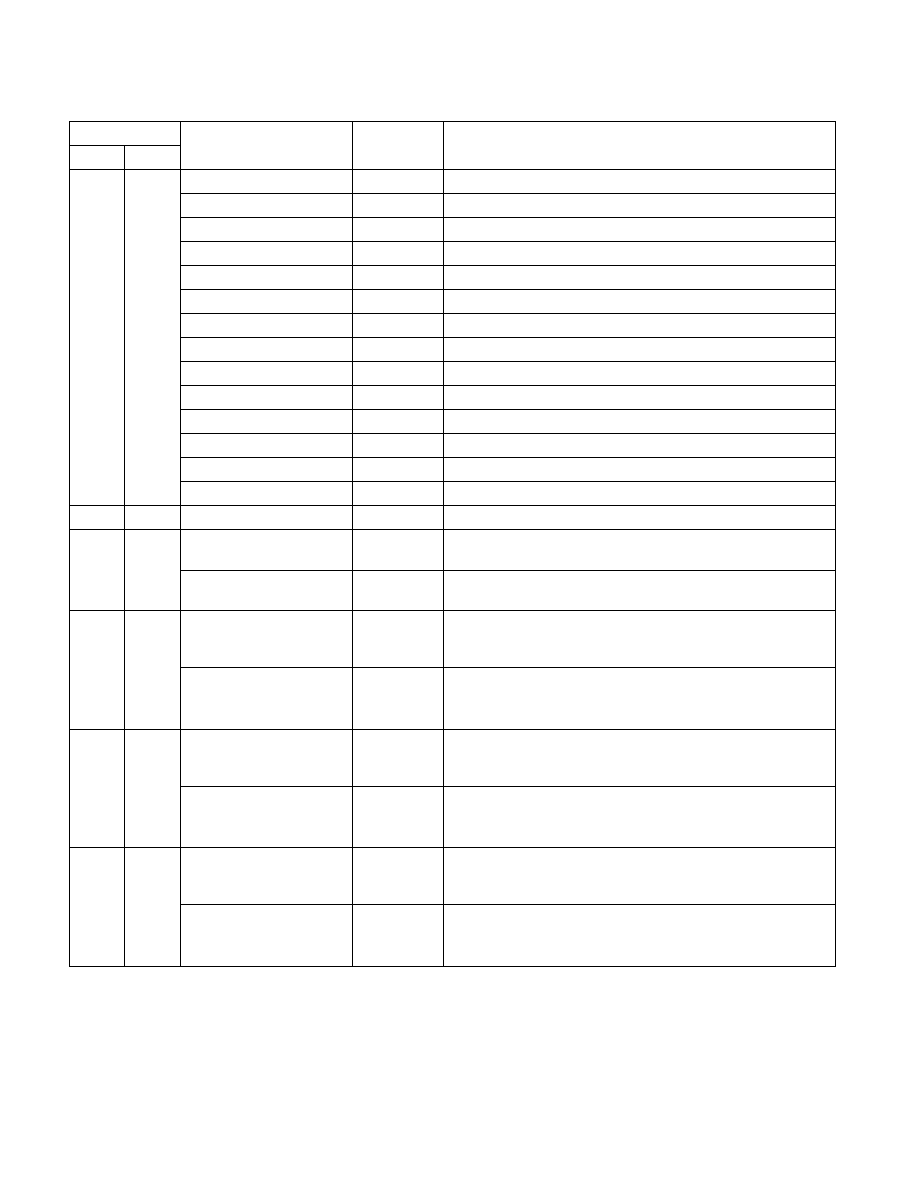

Vol. 3C 35-93

MODEL-SPECIFIC REGISTERS (MSRS)

3

Set 1 to cause Ovf_PMC3 = 1

31:4

Reserved.

32

Set 1 to cause Ovf_FixedCtr0 = 1

33

Set 1 to cause Ovf_FixedCtr1 = 1

34

Set 1 to cause Ovf_FixedCtr2 = 1

54:35

Reserved.

55

Set 1 to cause Trace_ToPA_PMI = 1

57:56

Reserved.

58

Set 1 to cause LBR_Frz = 1

59

Set 1 to cause CTR_Frz = 1

60

Set 1 to cause ASCI = 1

61

Set 1 to cause Ovf_Uncore

62

Set 1 to cause Ovf_BufDSSAVE

63

Reserved.

392H

914

IA32_PERF_GLOBAL_INUSE

3F1H

1009

MSR_PEBS_ENABLE

Core

See Table 35-2. See Section 18.4.4, “Precise Event Based Sampling

0

Enable PEBS trigger and recording for the programmed event

(precise or otherwise) on IA32_PMC0. (R/W)

3F8H

1016

MSR_PKG_C3_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

Package C3 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C3

states. Count at the same frequency as the TSC.

3F9H

1017

MSR_PKG_C6_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

Package C6 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C6

states. Count at the same frequency as the TSC.

3FCH

1020

MSR_CORE_C3_RESIDENCY Core

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

63:0

CORE C3 Residency Counter. (R/O)

Value since last reset that this core is in processor-specific C3

states. Count at the same frequency as the TSC.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec