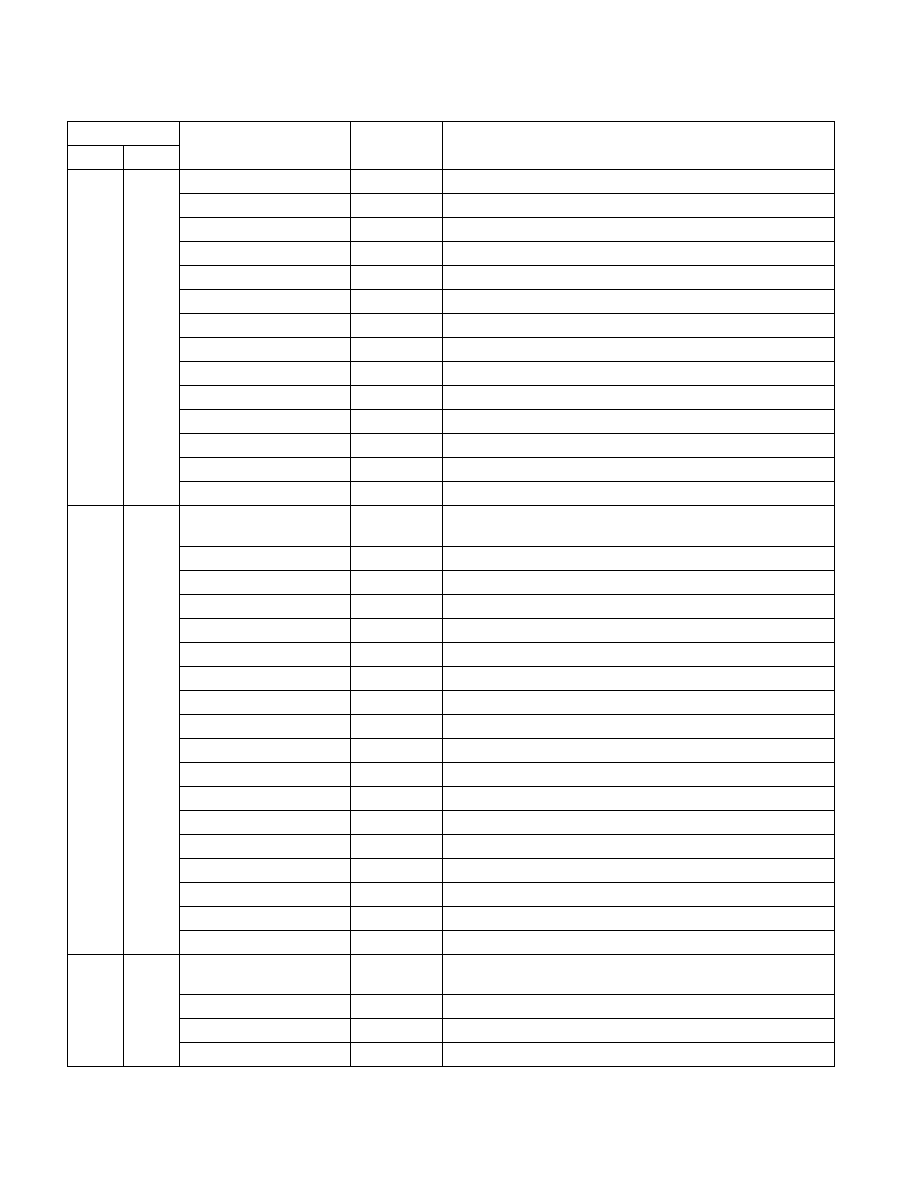

35-92 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

3

Ovf_PMC3

31:4

Reserved.

32

Ovf_FixedCtr0

33

Ovf_FixedCtr1

34

Ovf_FixedCtr2

54:35

Reserved.

55

Trace_ToPA_PMI.

57:56

Reserved.

58

LBR_Frz.

59

CTR_Frz.

60

ASCI.

61

Ovf_Uncore

62

Ovf_BufDSSAVE

63

CondChgd

390H

912

IA32_PERF_GLOBAL_STAT

US_RESET

Core

See Table 35-2. See Section 18.2.2.3, тАЬFull-Width Writes to

Performance Counter Registers.тАЭ

0

Set 1 to clear Ovf_PMC0

1

Set 1 to clear Ovf_PMC1

2

Set 1 to clear Ovf_PMC2

3

Set 1 to clear Ovf_PMC3

31:4

Reserved.

32

Set 1 to clear Ovf_FixedCtr0

33

Set 1 to clear Ovf_FixedCtr1

34

Set 1 to clear Ovf_FixedCtr2

54:35

Reserved.

55

Set 1 to clear Trace_ToPA_PMI.

57:56

Reserved.

58

Set 1 to clear LBR_Frz.

59

Set 1 to clear CTR_Frz.

60

Set 1 to clear ASCI.

61

Set 1 to clear Ovf_Uncore

62

Set 1 to clear Ovf_BufDSSAVE

63

Set 1 to clear CondChgd

391H

913

IA32_PERF_GLOBAL_STAT

US_SET

Core

See Table 35-2. See Section 18.2.2.3, тАЬFull-Width Writes to

Performance Counter Registers.тАЭ

0

Set 1 to cause Ovf_PMC0 = 1

1

Set 1 to cause Ovf_PMC1 = 1

2

Set 1 to cause Ovf_PMC2 = 1

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec