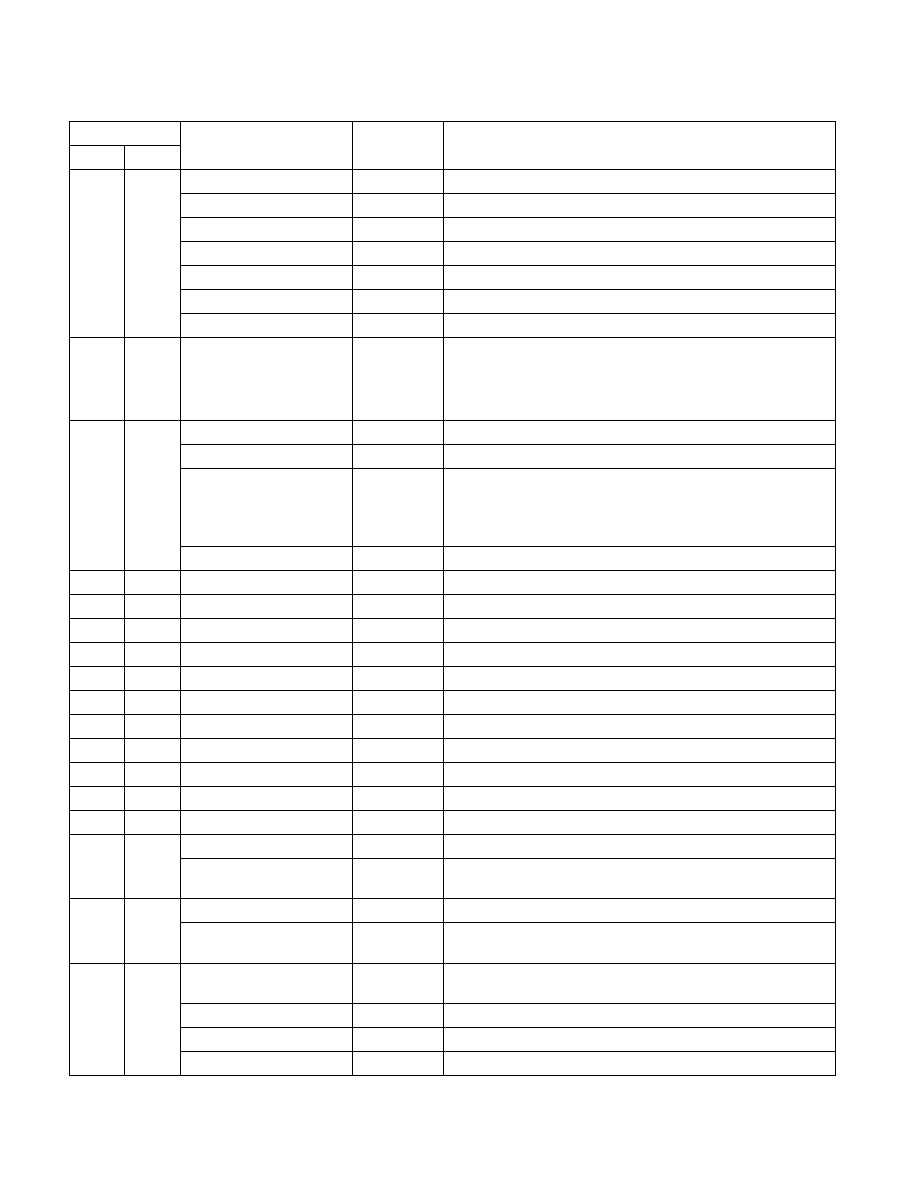

Vol. 3C 35-91

MODEL-SPECIFIC REGISTERS (MSRS)

4

NEAR_IND_CALL

5

NEAR_RET

6

NEAR_IND_JMP

7

NEAR_REL_JMP

8

FAR_BRANCH

9

EN_CALL_STACK

63:10

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Core

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-4) that points to the MSR containing the

most recent branch record.

See MSR_LASTBRANCH_0_FROM_IP.

1FCH

508

MSR_POWER_CTL

Core

Power Control Register. See http://biosbits.org.

0

Reserved.

1

Package

C1E Enable (R/W)

When set to тАШ1тАЩ, will enable the CPU to switch to the Minimum

Enhanced Intel SpeedStep Technology operating point when all

execution cores enter MWAIT (C1).

63:2

Reserved.

210H

528

IA32_MTRR_PHYSBASE8

Core

See Table 35-2.

211H

529

IA32_MTRR_PHYSMASK8

Core

See Table 35-2.

212H

530

IA32_MTRR_PHYSBASE9

Core

See Table 35-2.

213H

531

IA32_MTRR_PHYSMASK9

Core

See Table 35-2.

280H

640

IA32_MC0_CTL2

Module

See Table 35-2.

281H

641

IA32_MC1_CTL2

Module

See Table 35-2.

282H

642

IA32_MC2_CTL2

Core

See Table 35-2.

283H

643

IA32_MC3_CTL2

Module

See Table 35-2.

284H

644

IA32_MC4_CTL2

Package

285H

645

IA32_MC5_CTL2

Package

286H

646

IA32_MC6_CTL2

Package

300H

768

MSR_SGXOWNER0

Package

Lower 64 Bit OwnerEpoch Component of SGX Key (RO).

63:0

Low 64 bits of an 128-bit external entropy value for key

derivation of an enclave.

301H

769

MSR_SGXOWNER1

Package

Upper 64 Bit OwnerEpoch Component of SGX Key (RO).

63:0

Upper 64 bits of an 128-bit external entropy value for key

derivation of an enclave.

38EH

910

IA32_PERF_GLOBAL_

STATUS

Core

See Table 35-2. See Section 18.2.2.3, тАЬFull-Width Writes to

Performance Counter Registers.тАЭ

0

Ovf_PMC0

1

Ovf_PMC1

2

Ovf_PMC2

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec