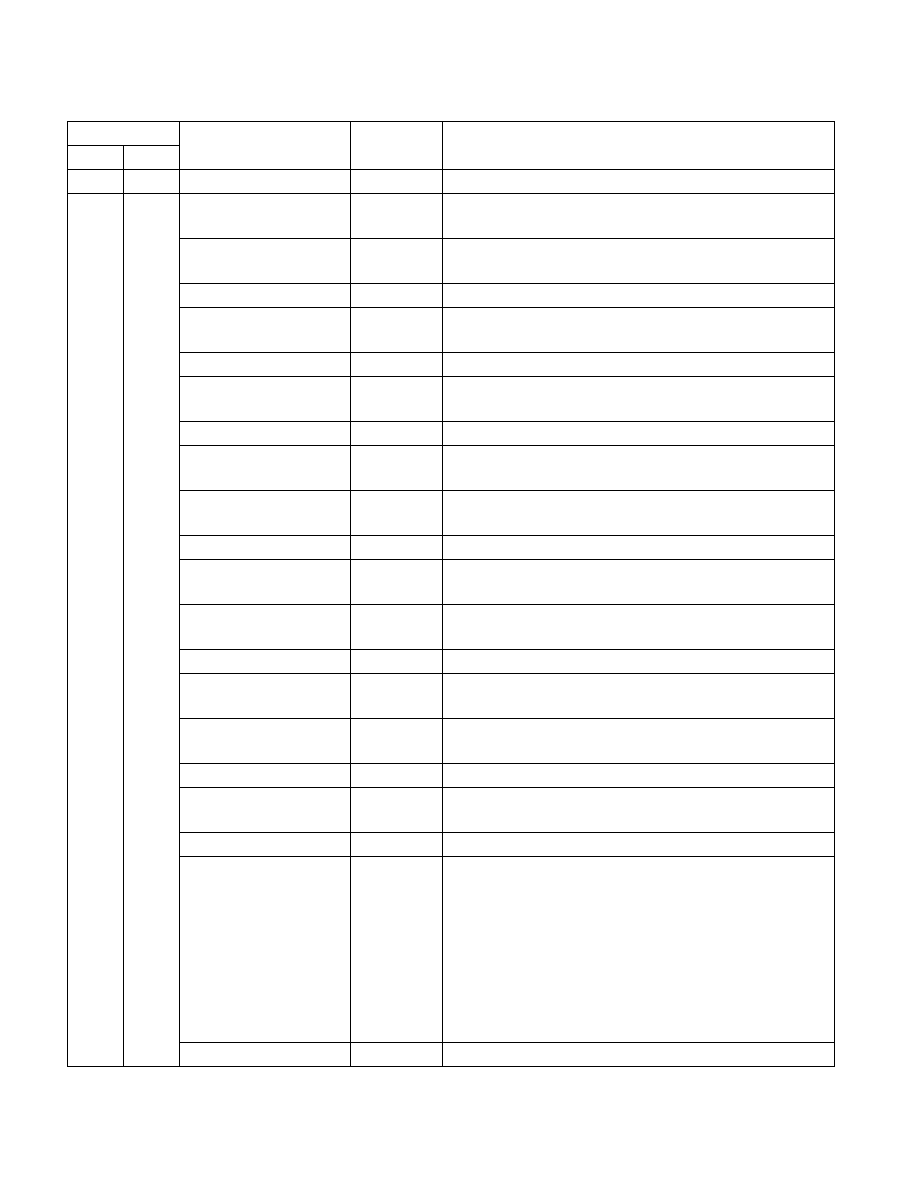

35-88 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

189H

393

IA32_PERFEVTSEL3

Core

See Table 35-2.

1A0H

416

IA32_MISC_ENABLE

Enable Misc. Processor Features (R/W)

Allows a variety of processor functions to be enabled and disabled.

0

Core

Fast-Strings Enable

See Table 35-2.

2:1

Reserved.

3

Package

Automatic Thermal Control Circuit Enable (R/W)

See Table 35-2. Default value is 1.

6:4

Reserved.

7

Core

Performance Monitoring Available (R)

See Table 35-2.

10:8

Reserved.

11

Core

Branch Trace Storage Unavailable (RO)

See Table 35-2.

12

Core

Processor Event Based Sampling Unavailable (RO)

See Table 35-2.

15:13

Reserved.

16

Package

Enhanced Intel SpeedStep Technology Enable (R/W)

See Table 35-2.

18

Core

ENABLE MONITOR FSM (R/W)

See Table 35-2.

21:19

Reserved.

22

Core

Limit CPUID Maxval (R/W)

See Table 35-2.

23

Package

xTPR Message Disable (R/W)

See Table 35-2.

33:24

Reserved.

34

Core

XD Bit Disable (R/W)

See Table 35-2.

37:35

Reserved.

38

Package

Turbo Mode Disable (R/W)

When set to 1 on processors that support Intel Turbo Boost

Technology, the turbo mode feature is disabled and the IDA_Enable

feature flag will be clear (CPUID.06H: EAX[1]=0).

When set to a 0 on processors that support IDA, CPUID.06H:

EAX[1] reports the processor’s support of turbo mode is enabled.

Note: the power-on default value is used by BIOS to detect

hardware support of turbo mode. If power-on default value is 1,

turbo mode is available in the processor. If power-on default value

is 0, turbo mode is not available.

63:39

Reserved.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec