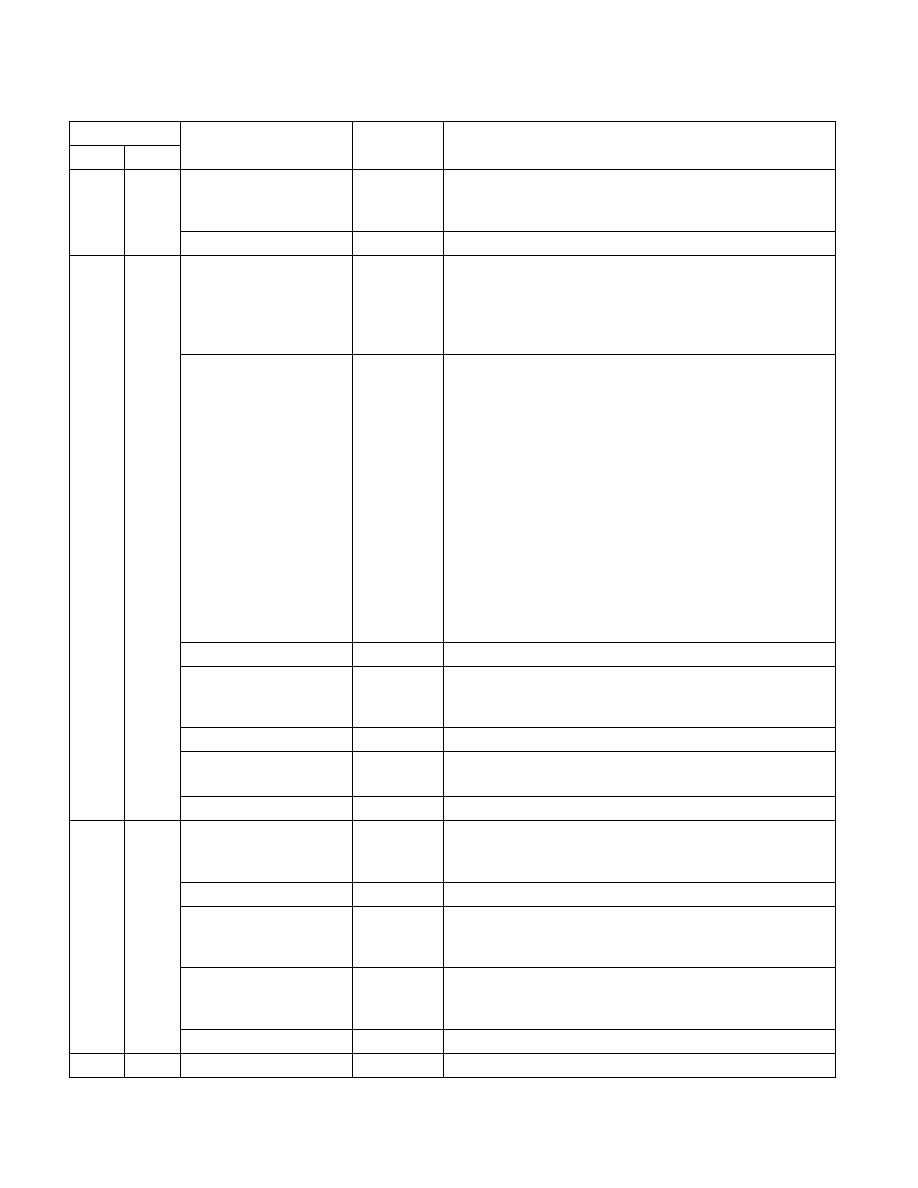

Vol. 3C 35-87

MODEL-SPECIFIC REGISTERS (MSRS)

47:40

Package

Maximum Efficiency Ratio (R/O)

The is the minimum ratio (maximum efficiency) that the processor

can operates, in units of 100MHz.

63:48

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

States.

See http://biosbits.org.

3:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power). for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

0000b: No limit

0001b: C1

0010b: C3

0011b: C6

0100b: C7

0101b: C7S

0110b: C8

0111b: C9

1000b: C10

9:3

Reserved.

10

I/O MWAIT Redirection Enable (R/W)

When set, will map IO_read instructions sent to IO register

specified by MSR_PMG_IO_CAPTURE_BASE to MWAIT instructions

14:11

Reserved.

15

CFG Lock (R/WO)

When set, lock bits 15:0 of this register until next reset.

63:16

Reserved.

17DH

381

MSR_SMM_MCA_CAP

Core

Enhanced SMM Capabilities (SMM-RO)

Reports SMM capability Enhancement. Accessible only while in

SMM.

57:0

Reserved

58

SMM_Code_Access_Chk (SMM-RO)

If set to 1 indicates that the SMM code access restriction is

supported and the MSR_SMM_FEATURE_CONTROL is supported.

59

Long_Flow_Indication (SMM-RO)

If set to 1 indicates that the SMM long flow indicator is supported

and the MSR_SMM_DELAYED is supported.

63:60

Reserved

188H

392

IA32_PERFEVTSEL2

Core

See Table 35-2.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec