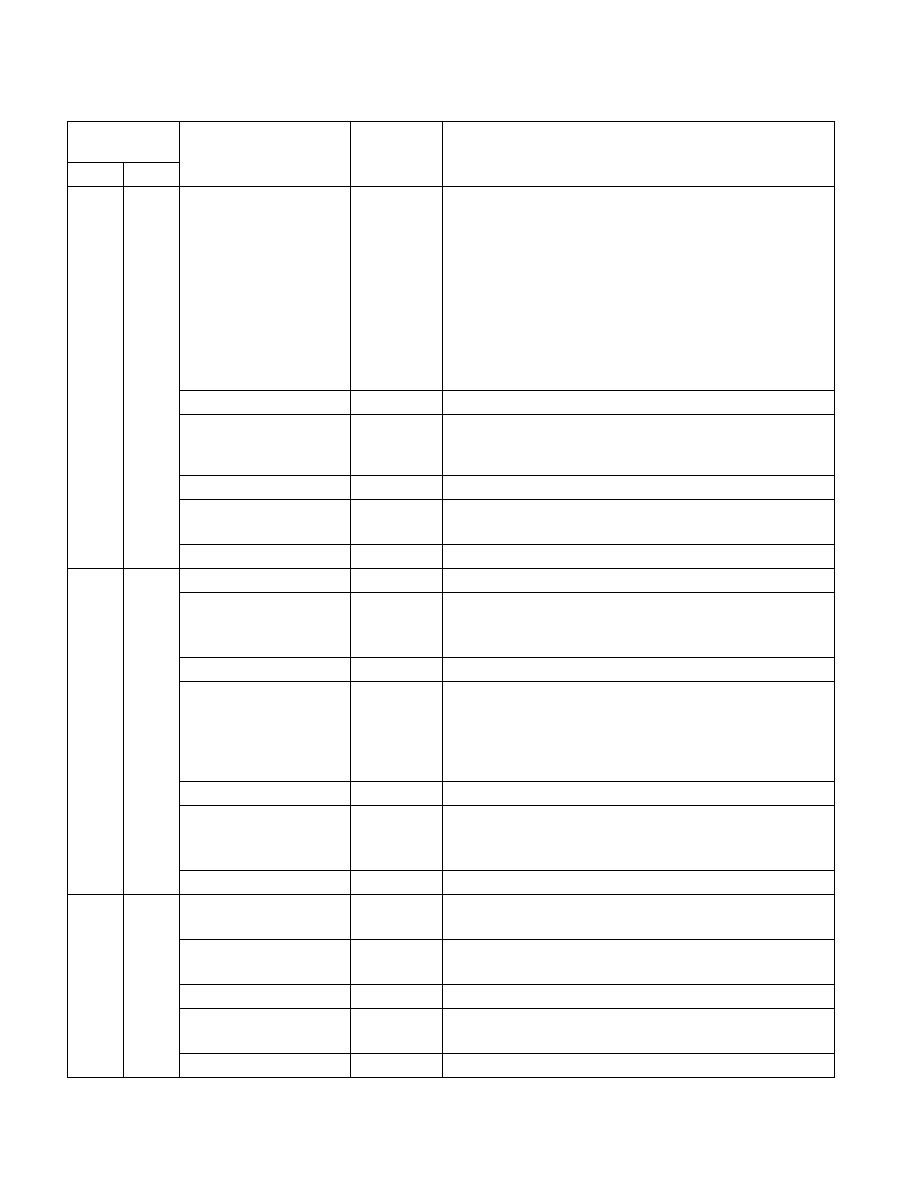

35-78 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

2:0

Package C-State Limit (R/W)

Specifies the lowest processor-specific C-state code name

(consuming the least power). for the package. The default is set as

factory-configured package C-state limit.

The following C-state code name encodings are supported:

000b: C0 (no package C-sate support)

001b: C1 (Behavior is the same as 000b)

100b: C4

110b: C6

111b: C7 (Silvermont only).

9:3

Reserved.

10

I/O MWAIT Redirection Enable (R/W)

When set, will map IO_read instructions sent to IO register

specified by MSR_PMG_IO_CAPTURE_BASE to MWAIT instructions

14:11

Reserved.

15

CFG Lock (R/WO)

When set, lock bits 15:0 of this register until next reset.

63:16

Reserved.

11EH

281

MSR_BBL_CR_CTL3

Module

0

L2 Hardware Enabled (RO)

1 = If the L2 is hardware-enabled

0 = Indicates if the L2 is hardware-disabled

7:1

Reserved.

8

L2 Enabled. (R/W)

1 = L2 cache has been initialized

0 = Disabled (default)

Until this bit is set the processor will not respond to the WBINVD

instruction or the assertion of the FLUSH# input.

22:9

Reserved.

23

L2 Not Present (RO)

0 = L2 Present

1 = L2 Not Present

63:24

Reserved.

1A0H

416

IA32_MISC_ENABLE

Enable Misc. Processor Features (R/W)

Allows a variety of processor functions to be enabled and disabled.

0

Core

Fast-Strings Enable

See Table 35-2.

2:1

Reserved.

3

Module

Automatic Thermal Control Circuit Enable (R/W)

See Table 35-2. Default value is 0.

6:4

Reserved.

Table 35-7. MSRs Common to the Silvermont and Airmont Microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec