Vol. 3C 35-71

MODEL-SPECIFIC REGISTERS (MSRS)

19BH

411

IA32_THERM_INTERRUPT

Core

Thermal Interrupt Control (R/W)

See Table 35-2.

19CH

412

IA32_THERM_STATUS

Core

Thermal Monitor Status (R/W)

See Table 35-2.

1A2H

418

MSR_

TEMPERATURE_TARGET

Package

15:0

Reserved.

23:16

Temperature Target (R)

The default thermal throttling or PROCHOT# activation

temperature in degree C, The effective temperature for thermal

throttling or PROCHOT# activation is “Temperature Target” +

“Target Offset”

29:24

Target Offset (R/W)

Specifies an offset in degrees C to adjust the throttling and

PROCHOT# activation temperature from the default target

specified in TEMPERATURE_TARGET (bits 23:16).

63:30

Reserved.

1A6H

422

MSR_OFFCORE_RSP_0

Module

Offcore Response Event Select Register (R/W)

1A7H

423

MSR_OFFCORE_RSP_1

Module

Offcore Response Event Select Register (R/W)

1B0H

432

IA32_ENERGY_PERF_BIAS

Core

See Table 35-2.

1D9H

473

IA32_DEBUGCTL

Core

Debug Control (R/W)

See Table 35-2.

1DDH

477

MSR_LER_FROM_LIP Core

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

1DEH

478

MSR_LER_TO_LIP

Core

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch

instruction that the processor executed prior to the last exception

that was generated or the last interrupt that was handled.

1F2H

498

IA32_SMRR_PHYSBASE

Core

See Table 35-2.

1F3H

499

IA32_SMRR_PHYSMASK

Core

See Table 35-2.

200H

512

IA32_MTRR_PHYSBASE0

Core

See Table 35-2.

201H

513

IA32_MTRR_PHYSMASK0

Core

See Table 35-2.

202H

514

IA32_MTRR_PHYSBASE1

Core

See Table 35-2.

203H

515

IA32_MTRR_PHYSMASK1

Core

See Table 35-2.

204H

516

IA32_MTRR_PHYSBASE2

Core

See Table 35-2.

205H

517

IA32_MTRR_PHYSMASK2

Core

See Table 35-2.

206H

518

IA32_MTRR_PHYSBASE3

Core

See Table 35-2.

207H

519

IA32_MTRR_PHYSMASK3

Core

See Table 35-2.

208H

520

IA32_MTRR_PHYSBASE4

Core

See Table 35-2.

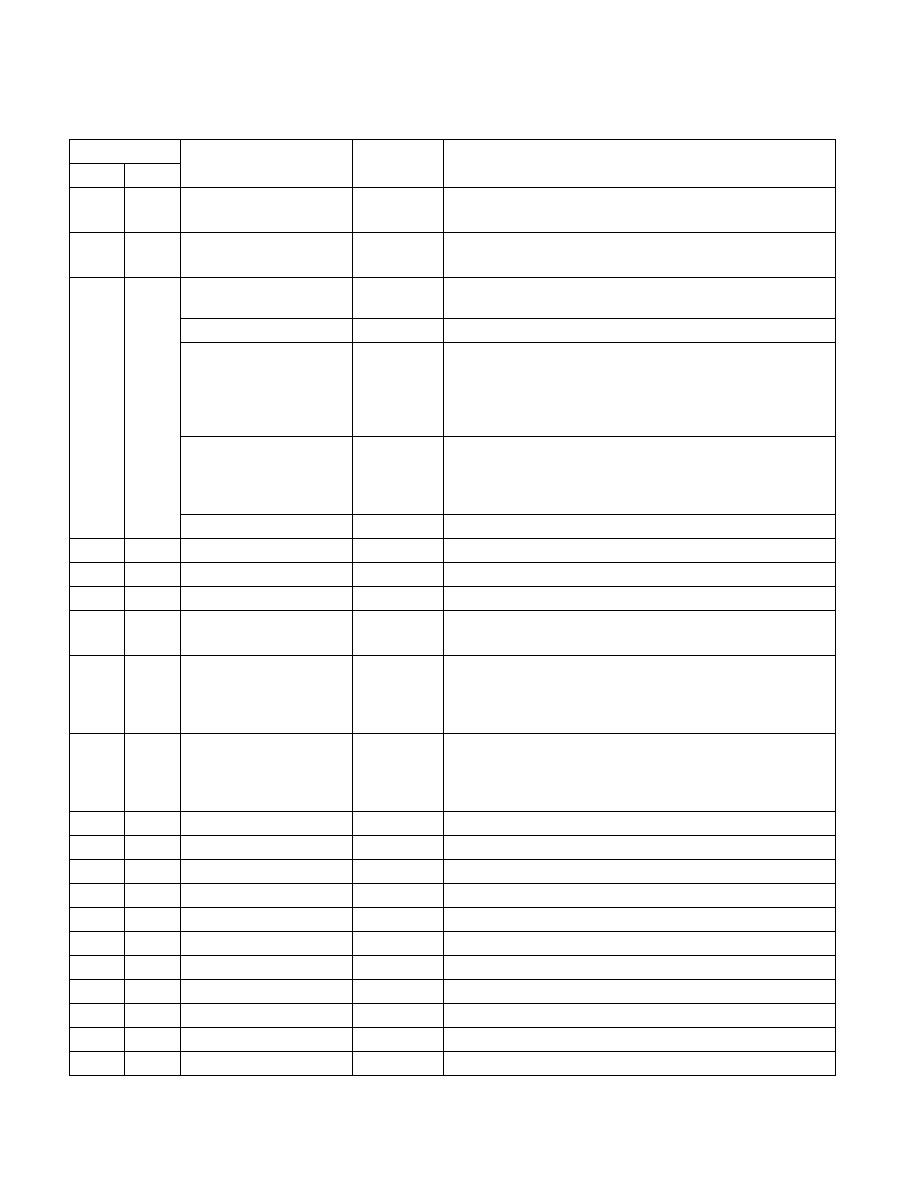

Table 35-6. MSRs Common to the Silvermont Microarchitecture and Newer Microarchitectures for Intel Atom

Processors

Address

Register Name

Scope

Bit Description

Hex

Dec