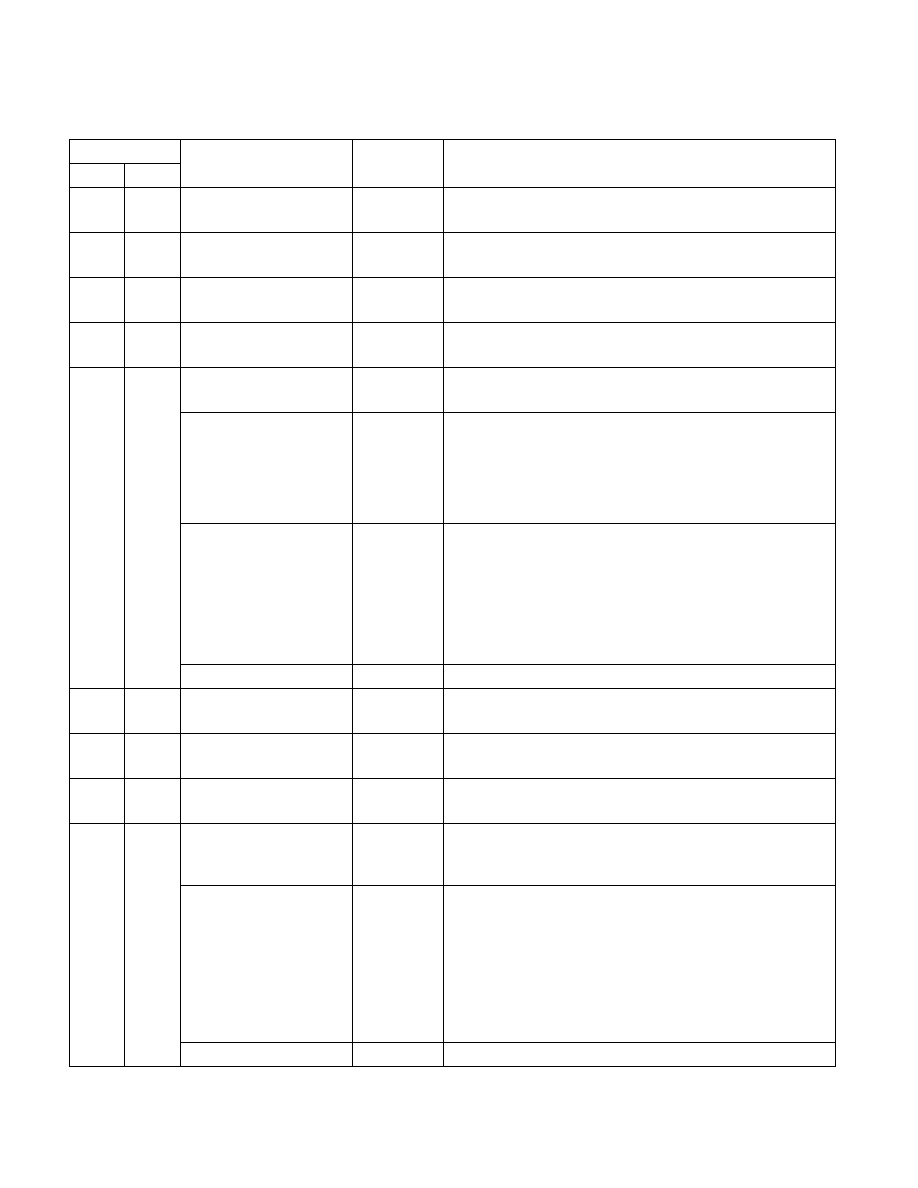

Vol. 3C 35-69

MODEL-SPECIFIC REGISTERS (MSRS)

79H

121

IA32_BIOS_UPDT_TRIG

Core

BIOS Update Trigger Register (W)

See Table 35-2.

8BH

139

IA32_BIOS_SIGN_ID

Core

BIOS Update Signature ID (RO)

See Table 35-2.

C1H

193

IA32_PMC0

Core

Performance counter register

See Table 35-2.

C2H

194

IA32_PMC1

Core

Performance Counter Register

See Table 35-2.

E4H

228

MSR_PMG_IO_CAPTURE_

BASE

Module

Power Management IO Redirection in C-state (R/W)

See http://biosbits.org.

15:0

LVL_2 Base Address (R/W)

Specifies the base address visible to software for IO redirection. If

IO MWAIT Redirection is enabled, reads to this address will be

consumed by the power management logic and decoded to MWAIT

instructions. When IO port address redirection is enabled, this is the

IO port address reported to the OS/software.

18:16

C-state Range (R/W)

Specifies the encoding value of the maximum C-State code name to

be included when IO read to MWAIT redirection is enabled by

MSR_PKG_CST_CONFIG_CONTROL[bit10]:

100b - C4 is the max C-State to include

110b - C6 is the max C-State to include

111b - C7 is the max C-State to include

63:19

Reserved.

E7H

231

IA32_MPERF

Core

Maximum Performance Frequency Clock Count (RW)

See Table 35-2.

E8H

232

IA32_APERF

Core

Actual Performance Frequency Clock Count (RW)

See Table 35-2.

FEH

254

IA32_MTRRCAP

Core

Memory Type Range Register (R)

See Table 35-2.

13CH

52

MSR_FEATURE_CONFIG

Core

AES Configuration (RW-L)

Privileged post-BIOS agent must provide a #GP handler to handle

unsuccessful read of this MSR.

1:0

AES Configuration (RW-L)

Upon a successful read of this MSR, the configuration of AES

instruction set availability is as follows:

11b: AES instructions are not available until next RESET.

otherwise, AES instructions are available.

Note, AES instruction set is not available if read is unsuccessful. If

the configuration is not 01b, AES instruction can be mis-configured

if a privileged agent unintentionally writes 11b.

63:2

Reserved.

Table 35-6. MSRs Common to the Silvermont Microarchitecture and Newer Microarchitectures for Intel Atom

Processors

Address

Register Name

Scope

Bit Description

Hex

Dec