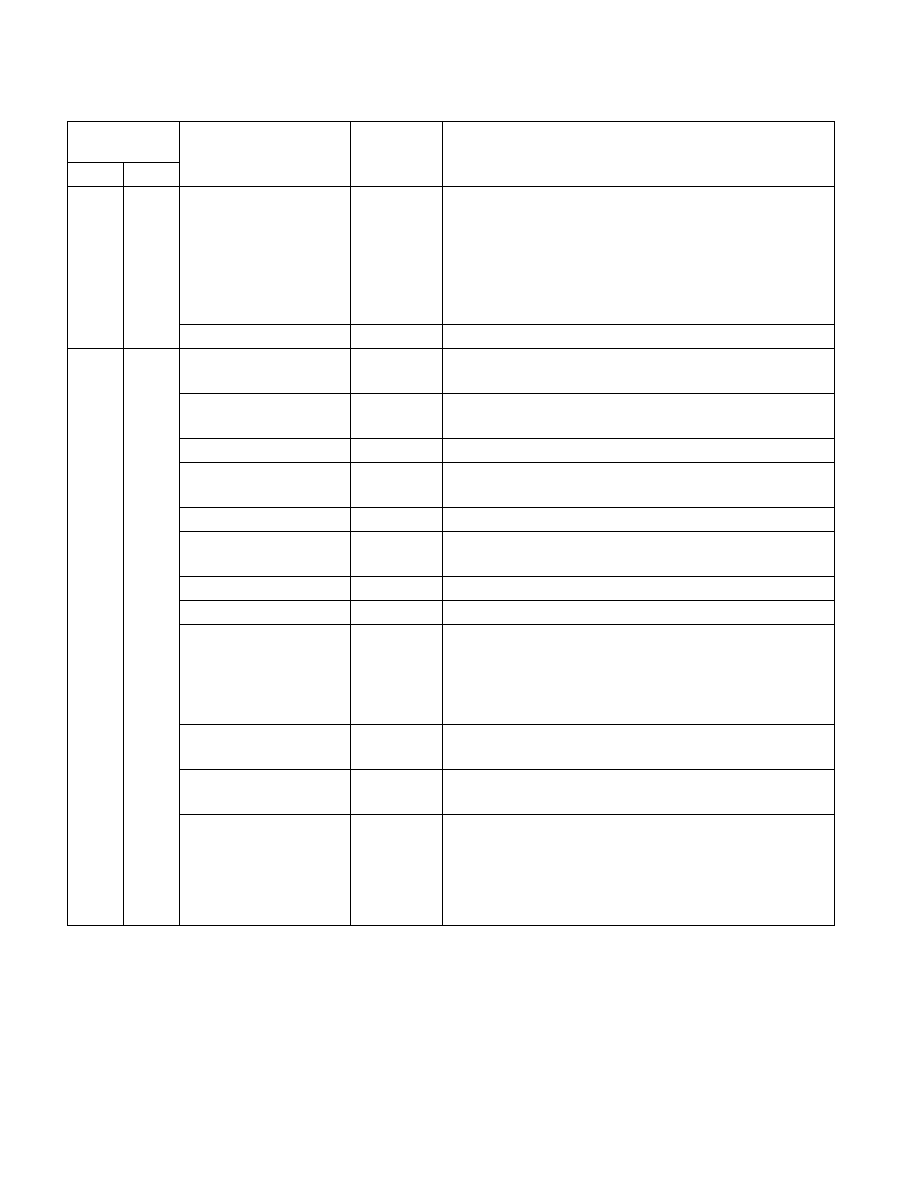

35-62 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

16

TM_SELECT (R/W)

Mode of automatic thermal monitor:

0 = Thermal Monitor 1 (thermally-initiated on-die modulation of

the stop-clock duty cycle)

1 = Thermal Monitor 2 (thermally-initiated frequency transitions)

If bit 3 of the IA32_MISC_ENABLE register is cleared, TM_SELECT

has no effect. Neither TM1 nor TM2 are enabled.

63:17

Reserved.

1A0H

416

IA32_MISC_ENABLE

Unique

Enable Misc. Processor Features (R/W)

Allows a variety of processor functions to be enabled and disabled.

0

Fast-Strings Enable

See Table 35-2.

2:1

Reserved.

3

Unique

Automatic Thermal Control Circuit Enable (R/W)

See Table 35-2. Default value is 0.

6:4

Reserved.

7

Shared

Performance Monitoring Available (R)

See Table 35-2.

8

Reserved.

9

Reserved.

10

Shared

FERR# Multiplexing Enable (R/W)

1 = FERR# asserted by the processor to indicate a pending break

event within the processor

0 = Indicates compatible FERR# signaling behavior

This bit must be set to 1 to support XAPIC interrupt model usage.

11

Shared

Branch Trace Storage Unavailable (RO)

See Table 35-2.

12

Shared

Processor Event Based Sampling Unavailable (RO)

See Table 35-2.

13

Shared

TM2 Enable (R/W)

When this bit is set (1) and the thermal sensor indicates that the

die temperature is at the pre-determined threshold, the Thermal

Monitor 2 mechanism is engaged. TM2 will reduce the bus to core

ratio and voltage according to the value last written to

MSR_THERM2_CTL bits 15:0.

Table 35-4. MSRs in 45 nm and 32 nm Intel® Atom™ Processor Family (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec