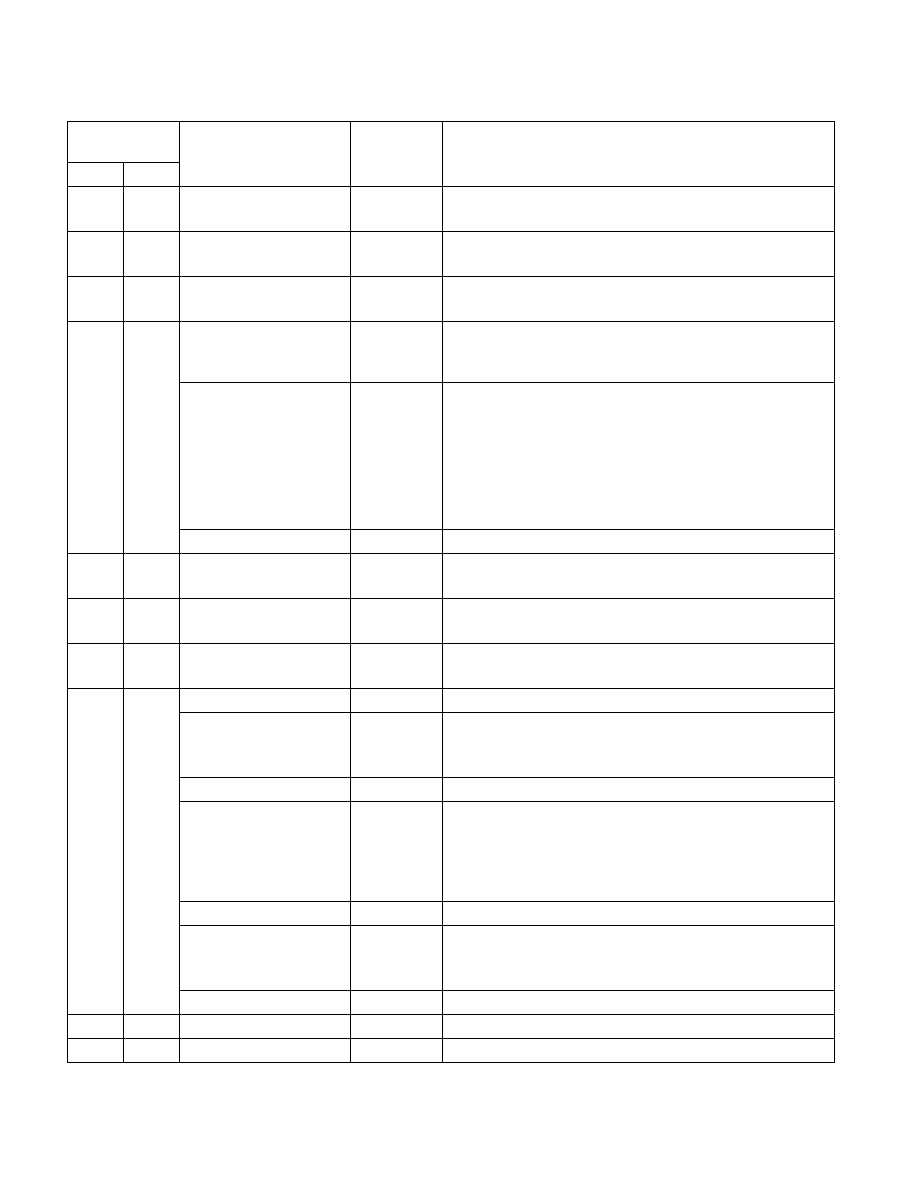

35-60 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

8BH

139

IA32_BIOS_SIGN_ID

Unique

BIOS Update Signature ID (RO)

See Table 35-2.

C1H

193

IA32_PMC0

Unique

Performance counter register

See Table 35-2.

C2H

194

IA32_PMC1

Unique

Performance Counter Register

See Table 35-2.

CDH

205

MSR_FSB_FREQ

Shared

Scaleable Bus Speed(RO)

This field indicates the intended scaleable bus clock speed for

processors based on Intel Atom microarchitecture:

2:0

• 111B: 083 MHz (FSB 333)

• 101B: 100 MHz (FSB 400)

• 001B: 133 MHz (FSB 533)

• 011B: 167 MHz (FSB 667)

133.33 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 001B.

166.67 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 011B.

63:3

Reserved.

E7H

231

IA32_MPERF

Unique

Maximum Performance Frequency Clock Count (RW)

See Table 35-2.

E8H

232

IA32_APERF

Unique

Actual Performance Frequency Clock Count (RW)

See Table 35-2.

FEH

254

IA32_MTRRCAP

Shared

Memory Type Range Register (R)

See Table 35-2.

11EH

281

MSR_BBL_CR_CTL3

Shared

0

L2 Hardware Enabled (RO)

1 = If the L2 is hardware-enabled

0 = Indicates if the L2 is hardware-disabled

7:1

Reserved.

8

L2 Enabled. (R/W)

1 = L2 cache has been initialized

0 = Disabled (default)

Until this bit is set the processor will not respond to the WBINVD

instruction or the assertion of the FLUSH# input.

22:9

Reserved.

23

L2 Not Present (RO)

0 = L2 Present

1 = L2 Not Present

63:24

Reserved.

174H

372

IA32_SYSENTER_CS

Unique

See Table 35-2.

175H

373

IA32_SYSENTER_ESP

Unique

See Table 35-2.

Table 35-4. MSRs in 45 nm and 32 nm Intel® Atom™ Processor Family (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec