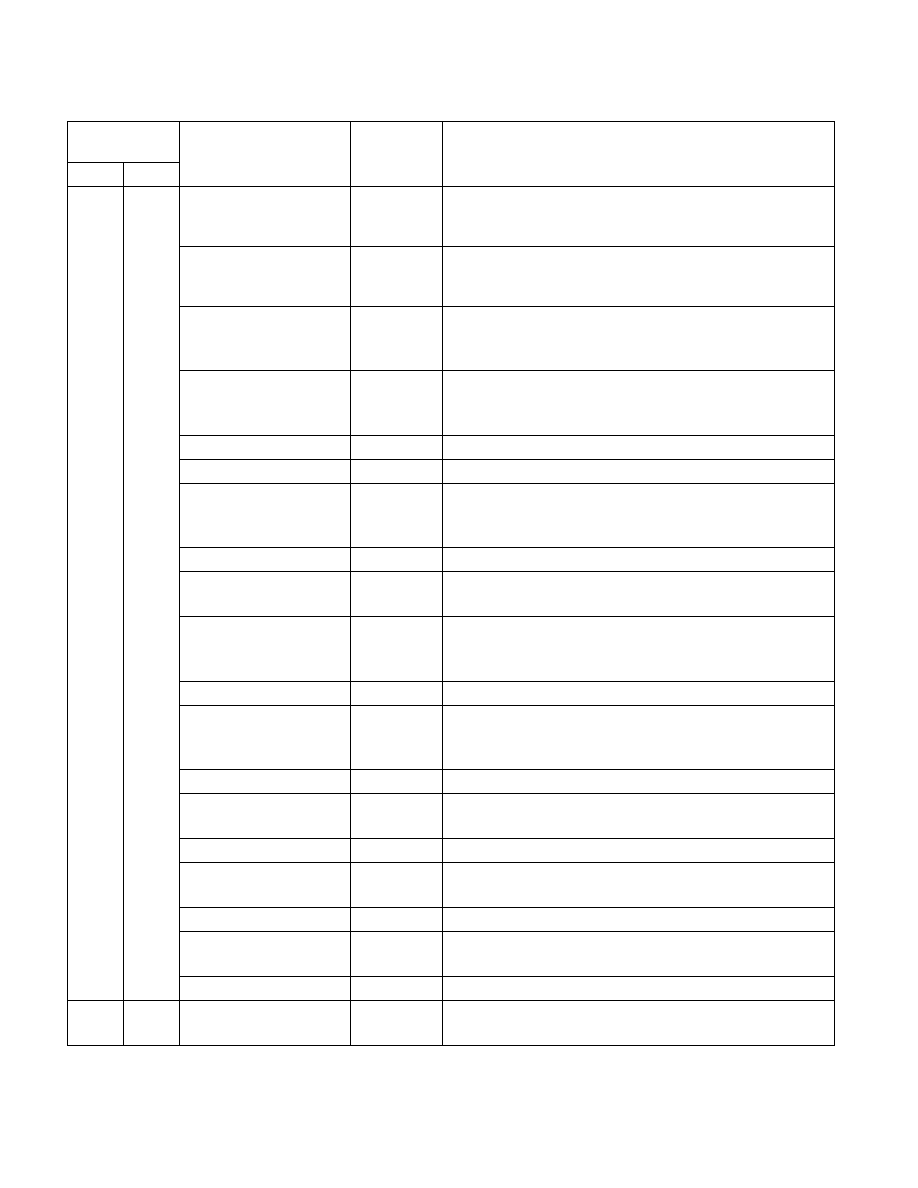

35-58 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

1

Data Error Checking Enable (R/W)

1 = Enabled; 0 = Disabled

Always 0.

2

Response Error Checking Enable (R/W)

1 = Enabled; 0 = Disabled

Always 0.

3

AERR# Drive Enable (R/W)

1 = Enabled; 0 = Disabled

Always 0.

4

BERR# Enable for initiator bus requests (R/W)

1 = Enabled; 0 = Disabled

Always 0.

5

Reserved.

6

Reserved.

7

BINIT# Driver Enable (R/W)

1 = Enabled; 0 = Disabled

Always 0.

8

Reserved.

9

Execute BIST (R/O)

1 = Enabled; 0 = Disabled

10

AERR# Observation Enabled (R/O)

1 = Enabled; 0 = Disabled

Always 0.

11

Reserved.

12

BINIT# Observation Enabled (R/O)

1 = Enabled; 0 = Disabled

Always 0.

13

Reserved.

14

1 MByte Power on Reset Vector (R/O)

1 = 1 MByte; 0 = 4 GBytes

15

Reserved

17:16

APIC Cluster ID (R/O)

Always 00B.

19: 18

Reserved.

21: 20

Symmetric Arbitration ID (R/O)

Always 00B.

26:22

Integer Bus Frequency Ratio (R/O)

3AH

58

IA32_FEATURE_CONTROL

Unique

Control Features in Intel 64Processor (R/W)

See Table 35-2.

Table 35-4. MSRs in 45 nm and 32 nm Intel® Atom™ Processor Family (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec