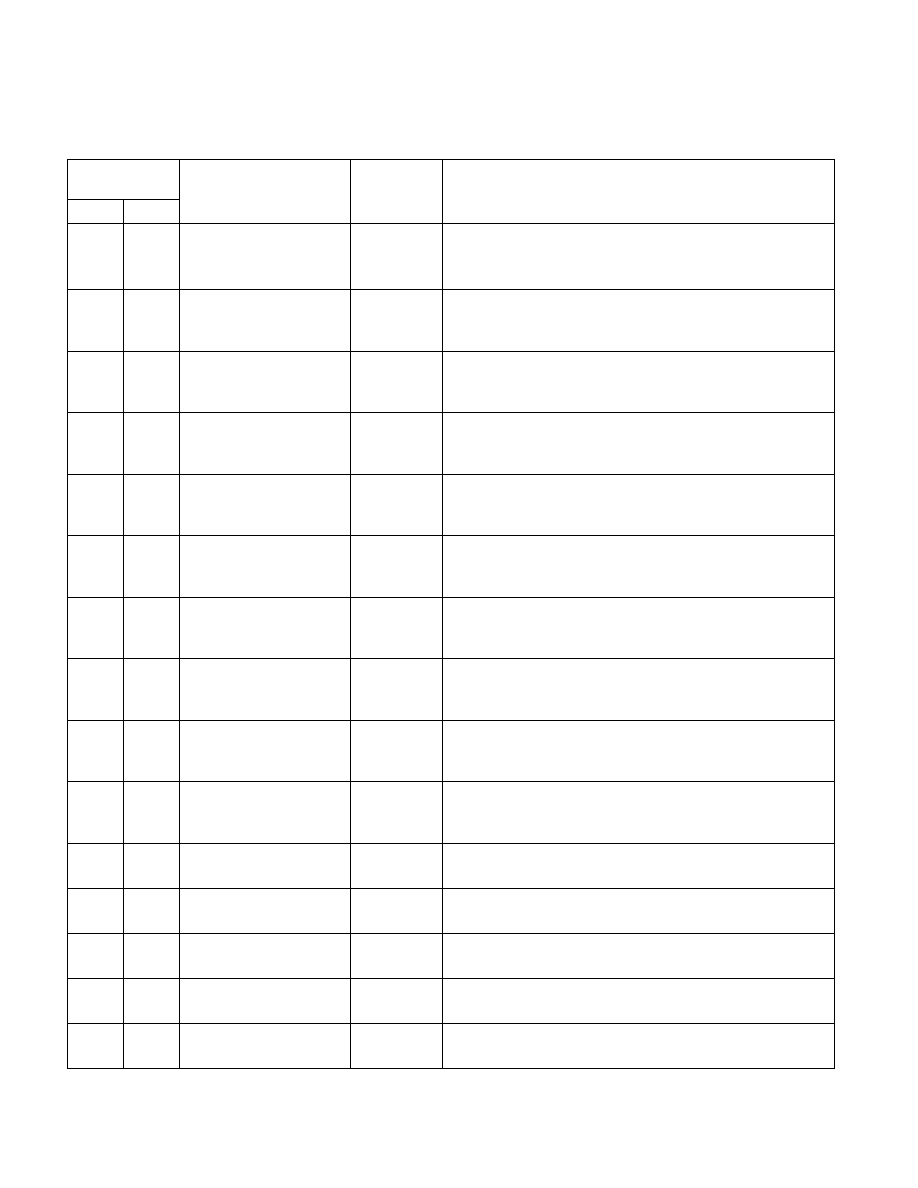

35-56 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

600H

1536

IA32_DS_AREA

Unique

DS Save Area (R/W)

See Table 35-2.

See Section 18.12.4, “Debug Store (DS) Mechanism.”

107CC

H

MSR_EMON_L3_CTR_CTL0

Unique

GBUSQ Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107CD

H

MSR_EMON_L3_CTR_CTL1

Unique

GBUSQ Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107CE

H

MSR_EMON_L3_CTR_CTL2

Unique

GSNPQ Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107CF

H

MSR_EMON_L3_CTR_CTL3

Unique

GSNPQ Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107D0

H

MSR_EMON_L3_CTR_CTL4

Unique

FSB Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107D1

H

MSR_EMON_L3_CTR_CTL5

Unique

FSB Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107D2

H

MSR_EMON_L3_CTR_CTL6

Unique

FSB Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107D3

H

MSR_EMON_L3_CTR_CTL7

Unique

FSB Event Control/Counter Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

107D8

H

MSR_EMON_L3_GL_CTL

Unique

L3/FSB Common Control Register (R/W)

Apply to Intel Xeon processor 7400 series (processor signature

06_1D) only. See Section 17.2.2

C000_

0080H

IA32_EFER

Unique

Extended Feature Enables

See Table 35-2.

C000_

0081H

IA32_STAR

Unique

System Call Target Address (R/W)

See Table 35-2.

C000_

0082H

IA32_LSTAR

Unique

IA-32e Mode System Call Target Address (R/W)

See Table 35-2.

C000_

0084H

IA32_FMASK

Unique

System Call Flag Mask (R/W)

See Table 35-2.

C000_

0100H

IA32_FS_BASE

Unique

Map of BASE Address of FS (R/W)

See Table 35-2.

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec