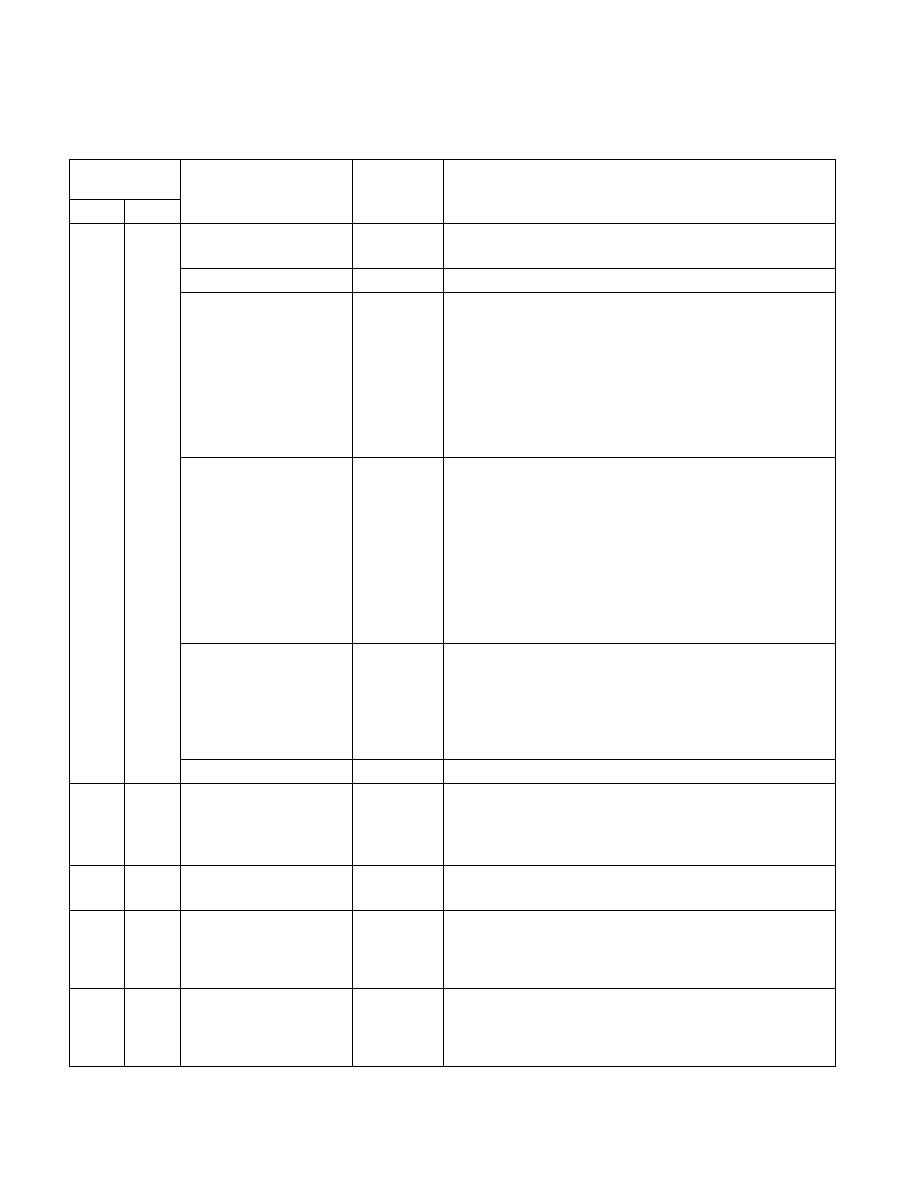

Vol. 3C 35-51

MODEL-SPECIFIC REGISTERS (MSRS)

34

Unique

XD Bit Disable (R/W)

See Table 35-2.

36:35

Reserved.

37

Unique

DCU Prefetcher Disable (R/W)

When set to 1, The DCU L1 data cache prefetcher is disabled. The

default value after reset is 0. BIOS may write ‘1’ to disable this

feature.

The DCU prefetcher is an L1 data cache prefetcher. When the DCU

prefetcher detects multiple loads from the same line done within a

time limit, the DCU prefetcher assumes the next line will be

required. The next line is prefetched in to the L1 data cache from

memory or L2.

38

Shared

IDA Disable (R/W)

When set to 1 on processors that support IDA, the Intel Dynamic

Acceleration feature (IDA) is disabled and the IDA_Enable feature

flag will be clear (CPUID.06H: EAX[1]=0).

When set to a 0 on processors that support IDA, CPUID.06H:

EAX[1] reports the processor’s support of IDA is enabled.

Note: the power-on default value is used by BIOS to detect

hardware support of IDA. If power-on default value is 1, IDA is

available in the processor. If power-on default value is 0, IDA is not

available.

39

Unique

IP Prefetcher Disable (R/W)

When set to 1, The IP prefetcher is disabled. The default value

after reset is 0. BIOS may write ‘1’ to disable this feature.

The IP prefetcher is an L1 data cache prefetcher. The IP prefetcher

looks for sequential load history to determine whether to prefetch

the next expected data into the L1 cache from memory or L2.

63:40

Reserved.

1C9H

457

MSR_LASTBRANCH_TOS

Unique

Last Branch Record Stack TOS (R/W)

Contains an index (bits 0-3) that points to the MSR containing the

most recent branch record.

See MSR_LASTBRANCH_0_FROM_IP (at 40H).

1D9H

473

IA32_DEBUGCTL

Unique

Debug Control (R/W)

See Table 35-2

1DDH

477

MSR_LER_FROM_LIP Unique

Last Exception Record From Linear IP (R)

Contains a pointer to the last branch instruction that the processor

executed prior to the last exception that was generated or the last

interrupt that was handled.

1DEH

478

MSR_LER_TO_LIP

Unique

Last Exception Record To Linear IP (R)

This area contains a pointer to the target of the last branch

instruction that the processor executed prior to the last exception

that was generated or the last interrupt that was handled.

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec