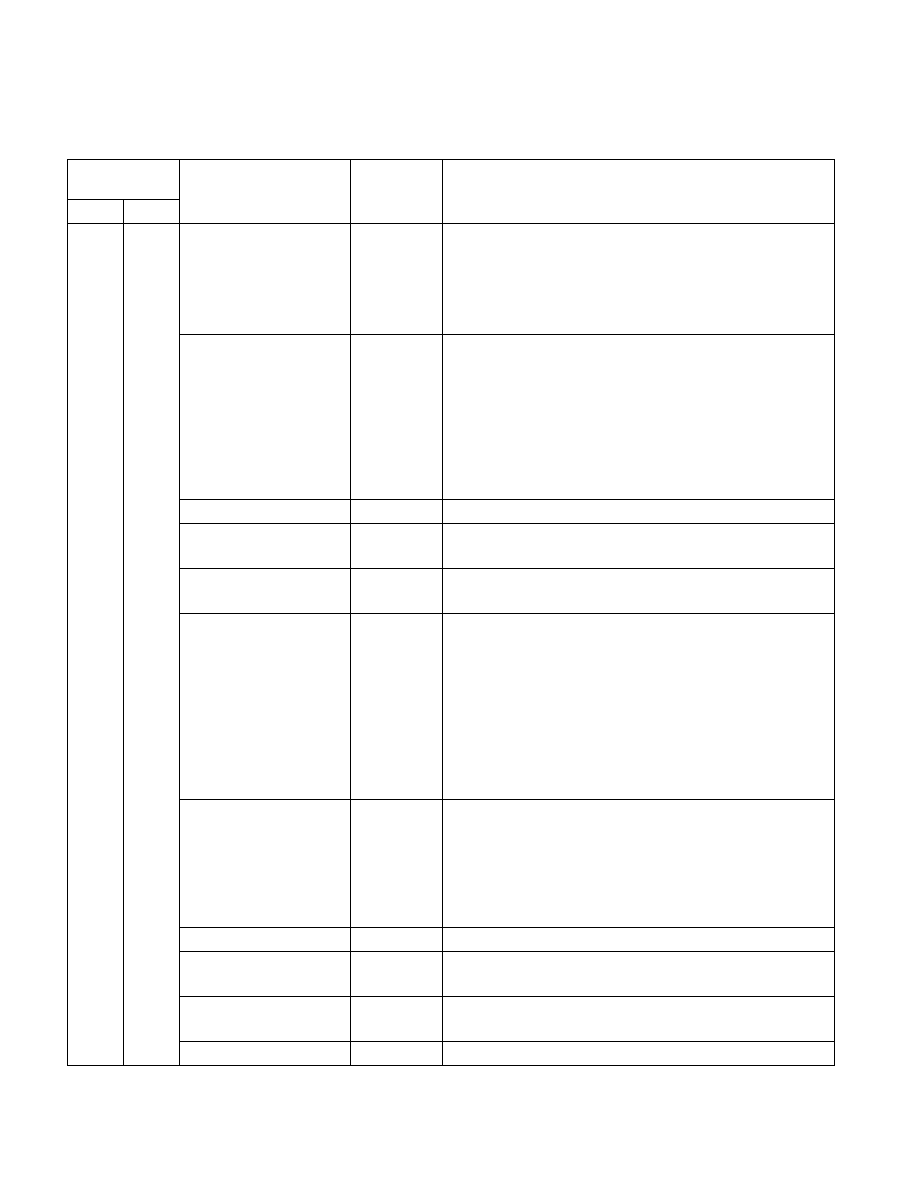

35-50 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

13

Shared

TM2 Enable (R/W)

When this bit is set (1) and the thermal sensor indicates that the

die temperature is at the pre-determined threshold, the Thermal

Monitor 2 mechanism is engaged. TM2 will reduce the bus to core

ratio and voltage according to the value last written to

MSR_THERM2_CTL bits 15:0.

When this bit is clear (0, default), the processor does not change

the VID signals or the bus to core ratio when the processor enters

a thermally managed state.

The BIOS must enable this feature if the TM2 feature flag

(CPUID.1:ECX[8]) is set; if the TM2 feature flag is not set, this

feature is not supported and BIOS must not alter the contents of

the TM2 bit location.

The processor is operating out of specification if both this bit and

the TM1 bit are set to 0.

15:14

Reserved.

16

Shared

Enhanced Intel SpeedStep Technology Enable (R/W)

See Table 35-2.

18

Shared

ENABLE MONITOR FSM (R/W)

See Table 35-2.

19

Shared

Adjacent Cache Line Prefetch Disable (R/W)

When set to 1, the processor fetches the cache line that contains

data currently required by the processor. When set to 0, the

processor fetches cache lines that comprise a cache line pair (128

bytes).

Single processor platforms should not set this bit. Server platforms

should set or clear this bit based on platform performance

observed in validation and testing.

BIOS may contain a setup option that controls the setting of this

bit.

20

Shared

Enhanced Intel SpeedStep Technology Select Lock (R/WO)

When set, this bit causes the following bits to become read-only:

• Enhanced Intel SpeedStep Technology Select Lock (this bit),

• Enhanced Intel SpeedStep Technology Enable bit.

The bit must be set before an Enhanced Intel SpeedStep

Technology transition is requested. This bit is cleared on reset.

21

Reserved.

22

Shared

Limit CPUID Maxval (R/W)

See Table 35-2.

23

Shared

xTPR Message Disable (R/W)

See Table 35-2.

33:24

Reserved.

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec