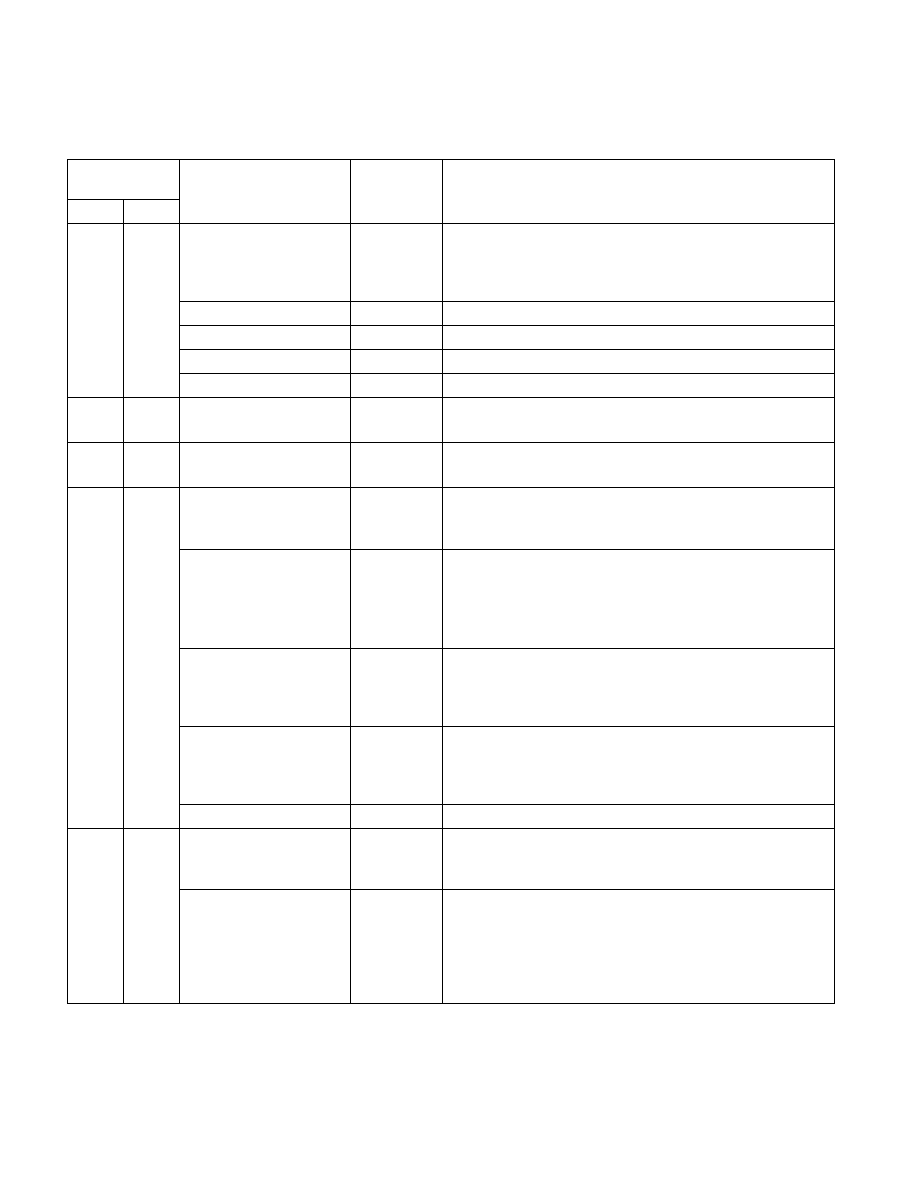

35-46 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

A1H

161

MSR_SMRR_PHYSMASK

Unique

System Management Mode Physical Address Mask register

(WO in SMM)

Model-specific implementation of SMRR-like interface, read visible

and write only in SMM.

10:0

Reserved.

11

Valid. Physical address base and range mask are valid.

31:12

PhysMask. SMRR physical address range mask.

63:32

Reserved.

C1H

193

IA32_PMC0

Unique

Performance Counter Register

See Table 35-2.

C2H

194

IA32_PMC1

Unique

Performance Counter Register

See Table 35-2.

CDH

205

MSR_FSB_FREQ

Shared

Scaleable Bus Speed(RO)

This field indicates the intended scaleable bus clock speed for

processors based on Intel Core microarchitecture:

2:0

• 101B: 100 MHz (FSB 400)

• 001B: 133 MHz (FSB 533)

• 011B: 167 MHz (FSB 667)

• 010B: 200 MHz (FSB 800)

• 000B: 267 MHz (FSB 1067)

• 100B: 333 MHz (FSB 1333)

133.33 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 001B.

166.67 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 011B.

266.67 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 000B.

333.33 MHz should be utilized if performing calculation with

System Bus Speed when encoding is 100B.

63:3

Reserved.

CDH

205

MSR_FSB_FREQ

Shared

Scaleable Bus Speed(RO)

This field indicates the intended scaleable bus clock speed for

processors based on Enhanced Intel Core microarchitecture:

2:0

• 101B: 100 MHz (FSB 400)

• 001B: 133 MHz (FSB 533)

• 011B: 167 MHz (FSB 667)

• 010B: 200 MHz (FSB 800)

• 000B: 267 MHz (FSB 1067)

• 100B: 333 MHz (FSB 1333)

• 110B: 400 MHz (FSB 1600)

Table 35-3. MSRs in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec