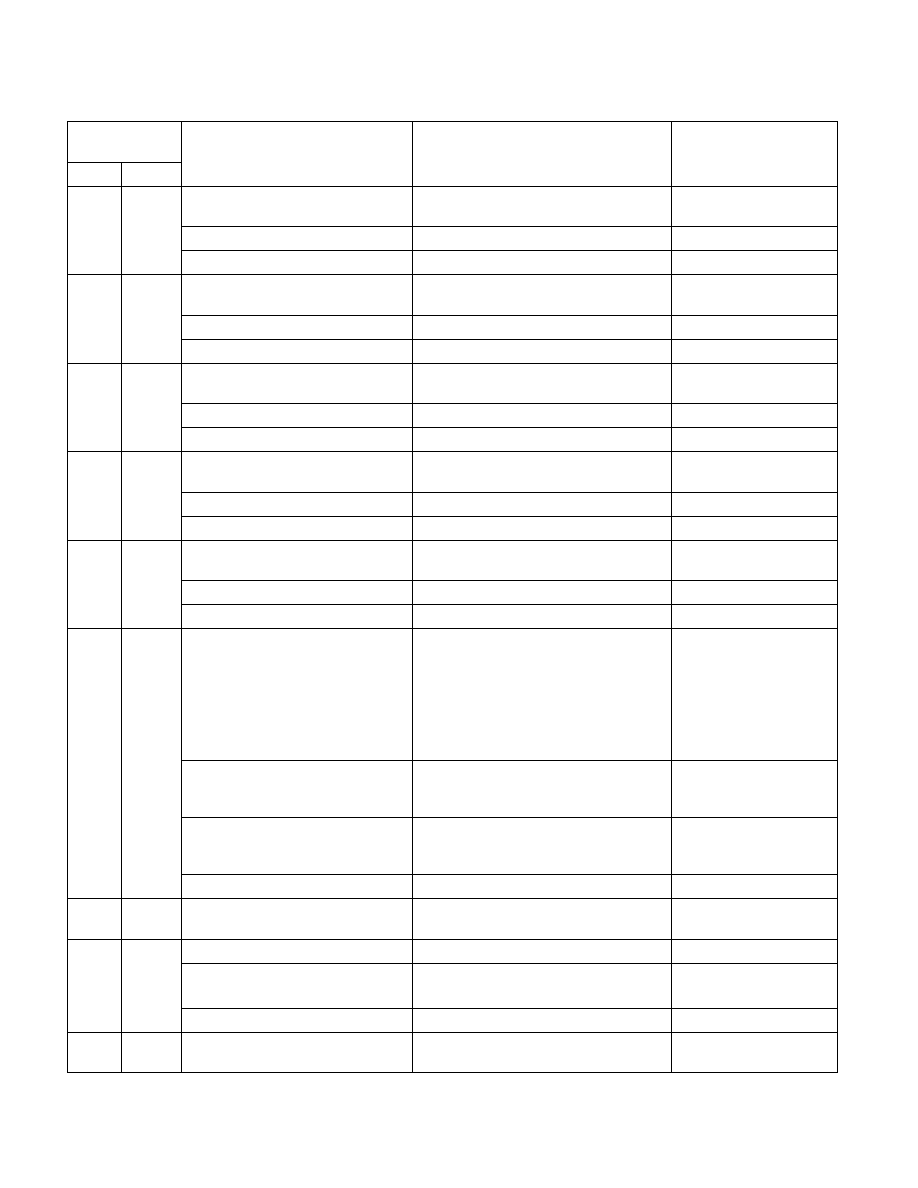

35-34 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

583H

1411

IA32_RTIT_ADDR1_B

Region 1 End Address (R/W)

If (CPUID.(EAX=07H,

ECX=1):EAX[2:0] > 1)

47:0

Virtual Address

63:48

SignExt_VA

584H

1412

IA32_RTIT_ADDR2_A

Region 2 Start Address (R/W)

If (CPUID.(EAX=07H,

ECX=1):EAX[2:0] > 2)

47:0

Virtual Address

63:48

SignExt_VA

585H

1413

IA32_RTIT_ADDR2_B

Region 2 End Address (R/W)

If (CPUID.(EAX=07H,

ECX=1):EAX[2:0] > 2)

47:0

Virtual Address

63:48

SignExt_VA

586H

1414

IA32_RTIT_ADDR3_A

Region 3 Start Address (R/W)

If (CPUID.(EAX=07H,

ECX=1):EAX[2:0] > 3)

47:0

Virtual Address

63:48

SignExt_VA

587H

1415

IA32_RTIT_ADDR3_B

Region 3 End Address (R/W)

If (CPUID.(EAX=07H,

ECX=1):EAX[2:0] > 3)

47:0

Virtual Address

63:48

SignExt_VA

600H

1536

IA32_DS_AREA

DS Save Area (R/W)

Points to the linear address of the first

byte of the DS buffer management area,

which is used to manage the BTS and PEBS

buffers.

See Section 18.12.4, “Debug Store (DS)

If( CPUID.01H:EDX.DS[21]

= 1

63:0

The linear address of the first byte of the

DS buffer management area, if IA-32e

mode is active.

31:0

The linear address of the first byte of the

DS buffer management area, if not in IA-

32e mode.

63:32

Reserved if not in IA-32e mode.

6E0H

1760

IA32_TSC_DEADLINE

TSC Target of Local APIC’s TSC Deadline

Mode (R/W)

If CPUID.01H:ECX.[24] = 1

770H

1904

IA32_PM_ENABLE

Enable/disable HWP (R/W)

If CPUID.06H:EAX.[7] = 1

0

HWP_ENABLE (R/W1-Once).

See Section 14.4.2, “Enabling HWP”

If CPUID.06H:EAX.[7] = 1

63:1

Reserved.

771H

1905

IA32_HWP_CAPABILITIES

HWP Performance Range Enumeration

(RO)

If CPUID.06H:EAX.[7] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal