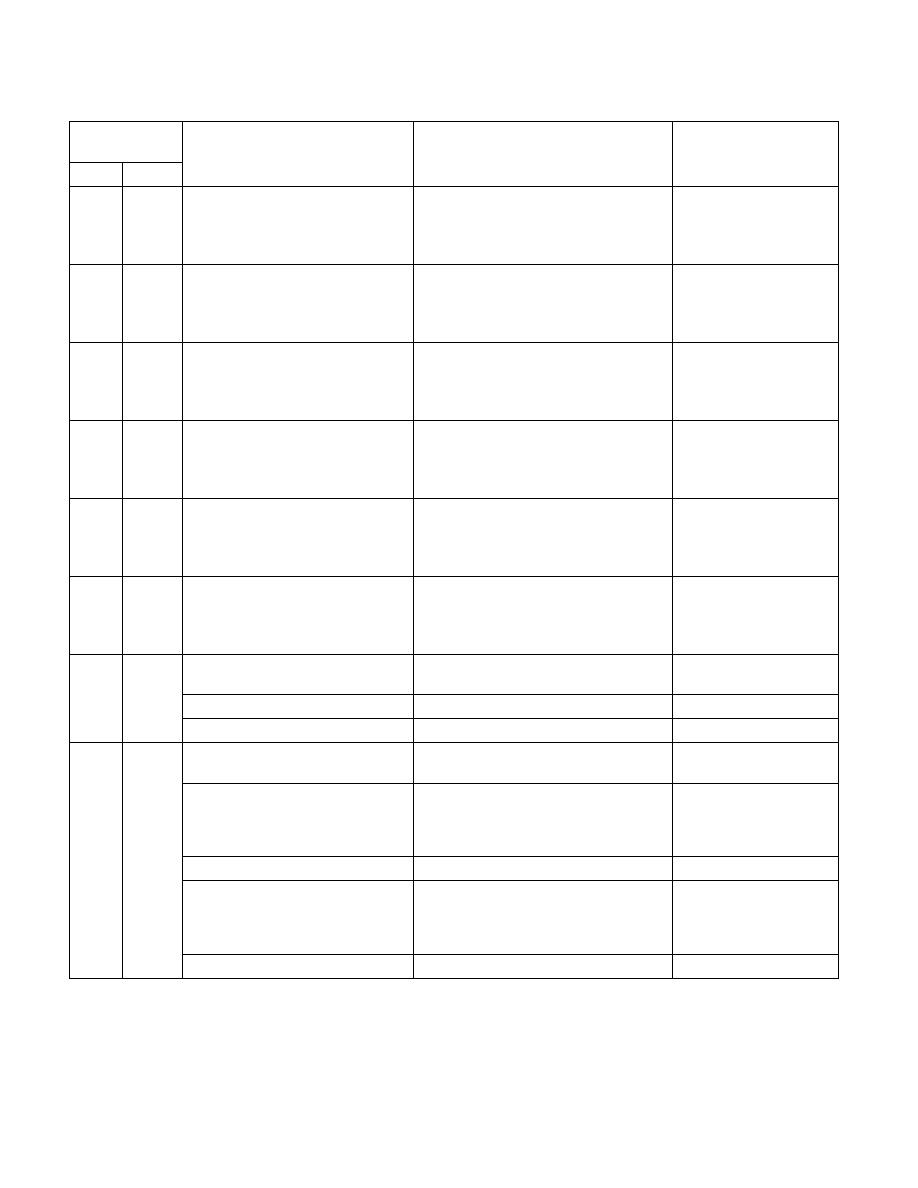

Vol. 3C 35-31

MODEL-SPECIFIC REGISTERS (MSRS)

4C3H

1219

IA32_A_PMC2

Full Width Writable IA32_PMC2 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

2) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C4H

1220

IA32_A_PMC3

Full Width Writable IA32_PMC3 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

3) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C5H

1221

IA32_A_PMC4

Full Width Writable IA32_PMC4 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

4) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C6H

1222

IA32_A_PMC5

Full Width Writable IA32_PMC5 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

5) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C7H

1223

IA32_A_PMC6

Full Width Writable IA32_PMC6 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

6) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C8H

1224

IA32_A_PMC7

Full Width Writable IA32_PMC7 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

7) &&

IA32_PERF_CAPABILITIES[

13] = 1

4D0H

1232

IA32_MCG_EXT_CTL

(R/W)

If IA32_MCG_CAP.LMCE_P

=1

0

LMCE_EN.

63:1

Reserved.

500H

1280

IA32_SGX_SVN_STATUS

Status and SVN Threshold of SGX Support

for ACM (RO).

If CPUID.(EAX=07H,

ECX=0H): EBX[2] = 1

0

Lock.

15:1

Reserved.

23:16

SGX_SVN_SINIT.

See Section 42.11.3,

63:24

Reserved.

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal