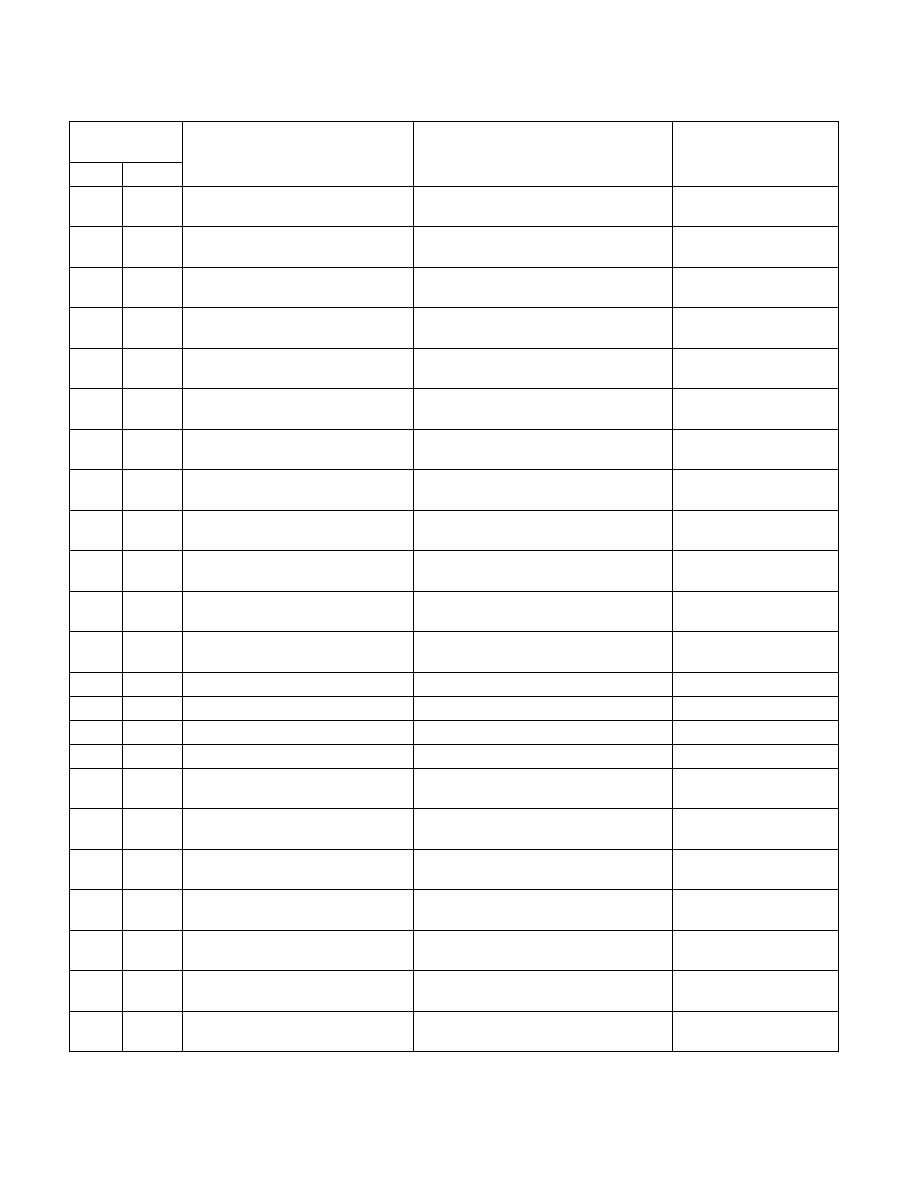

Vol. 3C 35-17

MODEL-SPECIFIC REGISTERS (MSRS)

204H

516

IA32_MTRR_PHYSBASE2

MTRRphysBase2

If CPUID.01H:

EDX.MTRR[12] =1

205H

517

IA32_MTRR_PHYSMASK2

MTRRphysMask2

If CPUID.01H:

EDX.MTRR[12] =1

206H

518

IA32_MTRR_PHYSBASE3

MTRRphysBase3

If CPUID.01H:

EDX.MTRR[12] =1

207H

519

IA32_MTRR_PHYSMASK3

MTRRphysMask3

If CPUID.01H:

EDX.MTRR[12] =1

208H

520

IA32_MTRR_PHYSBASE4

MTRRphysBase4

If CPUID.01H:

EDX.MTRR[12] =1

209H

521

IA32_MTRR_PHYSMASK4

MTRRphysMask4

If CPUID.01H:

EDX.MTRR[12] =1

20AH

522

IA32_MTRR_PHYSBASE5

MTRRphysBase5

If CPUID.01H:

EDX.MTRR[12] =1

20BH

523

IA32_MTRR_PHYSMASK5

MTRRphysMask5

If CPUID.01H:

EDX.MTRR[12] =1

20CH

524

IA32_MTRR_PHYSBASE6

MTRRphysBase6

If CPUID.01H:

EDX.MTRR[12] =1

20DH

525

IA32_MTRR_PHYSMASK6

MTRRphysMask6

If CPUID.01H:

EDX.MTRR[12] =1

20EH

526

IA32_MTRR_PHYSBASE7

MTRRphysBase7

If CPUID.01H:

EDX.MTRR[12] =1

20FH

527

IA32_MTRR_PHYSMASK7

MTRRphysMask7

If CPUID.01H:

EDX.MTRR[12] =1

210H

528

IA32_MTRR_PHYSBASE8

MTRRphysBase8

if IA32_MTRRCAP[7:0] > 8

211H

529

IA32_MTRR_PHYSMASK8

MTRRphysMask8

if IA32_MTRRCAP[7:0] > 8

212H

530

IA32_MTRR_PHYSBASE9

MTRRphysBase9

if IA32_MTRRCAP[7:0] > 9

213H

531

IA32_MTRR_PHYSMASK9

MTRRphysMask9

if IA32_MTRRCAP[7:0] > 9

250H

592

IA32_MTRR_FIX64K_00000

MTRRfix64K_00000

If CPUID.01H:

EDX.MTRR[12] =1

258H

600

IA32_MTRR_FIX16K_80000

MTRRfix16K_80000

If CPUID.01H:

EDX.MTRR[12] =1

259H

601

IA32_MTRR_FIX16K_A0000

MTRRfix16K_A0000

If CPUID.01H:

EDX.MTRR[12] =1

268H

616

IA32_MTRR_FIX4K_C0000

(MTRRfix4K_C0000 )

See Section 11.11.2.2, “Fixed Range

If CPUID.01H:

EDX.MTRR[12] =1

269H

617

IA32_MTRR_FIX4K_C8000

MTRRfix4K_C8000

If CPUID.01H:

EDX.MTRR[12] =1

26AH

618

IA32_MTRR_FIX4K_D0000

MTRRfix4K_D0000

If CPUID.01H:

EDX.MTRR[12] =1

26BH

619

IA32_MTRR_FIX4K_D8000

MTRRfix4K_D8000

If CPUID.01H:

EDX.MTRR[12] =1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal