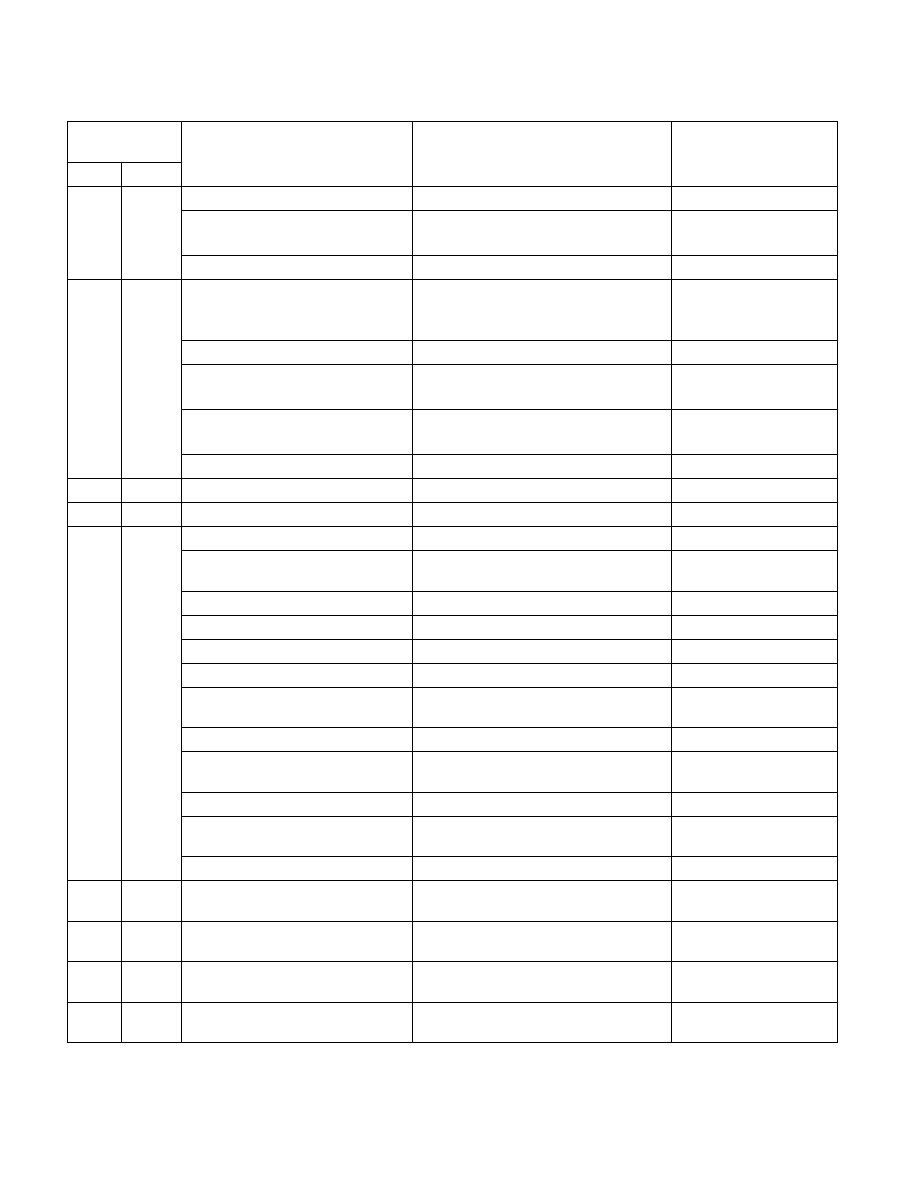

35-16 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

11:8

Reserved.

31:12

PhysBase.

SMRR physical Base Address.

63:32

Reserved.

1F3H

499

IA32_SMRR_PHYSMASK

SMRR Range Mask. (Writeable only in

SMM)

Range Mask of SMM memory range.

If IA32_MTRRCAP[SMRR]

= 1

10:0

Reserved.

11

Valid

Enable range mask.

31:12

PhysMask

SMRR address range mask.

63:32

Reserved.

1F8H

504

IA32_PLATFORM_DCA_CAP

DCA Capability (R)

If CPUID.01H: ECX[18] = 1

1F9H

505

IA32_CPU_DCA_CAP

If set, CPU supports Prefetch-Hint type.

If CPUID.01H: ECX[18] = 1

1FAH

506

IA32_DCA_0_CAP

DCA type 0 Status and Control register.

If CPUID.01H: ECX[18] = 1

0

DCA_ACTIVE: Set by HW when DCA is fuse-

enabled and no defeatures are set.

2:1

TRANSACTION

6:3

DCA_TYPE

10:7

DCA_QUEUE_SIZE

12:11

Reserved.

16:13

DCA_DELAY: Writes will update the register

but have no HW side-effect.

23:17

Reserved.

24

SW_BLOCK: SW can request DCA block by

setting this bit.

25

Reserved.

26

HW_BLOCK: Set when DCA is blocked by

HW (e.g. CR0.CD = 1).

31:27

Reserved.

200H

512

IA32_MTRR_PHYSBASE0

(MTRRphysBase0)

See Section 11.11.2.3, “Variable Range

If CPUID.01H:

EDX.MTRR[12] =1

201H

513

IA32_MTRR_PHYSMASK0

MTRRphysMask0

If CPUID.01H:

EDX.MTRR[12] =1

202H

514

IA32_MTRR_PHYSBASE1

MTRRphysBase1

If CPUID.01H:

EDX.MTRR[12] =1

203H

515

IA32_MTRR_PHYSMASK1

MTRRphysMask1

If CPUID.01H:

EDX.MTRR[12] =1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal