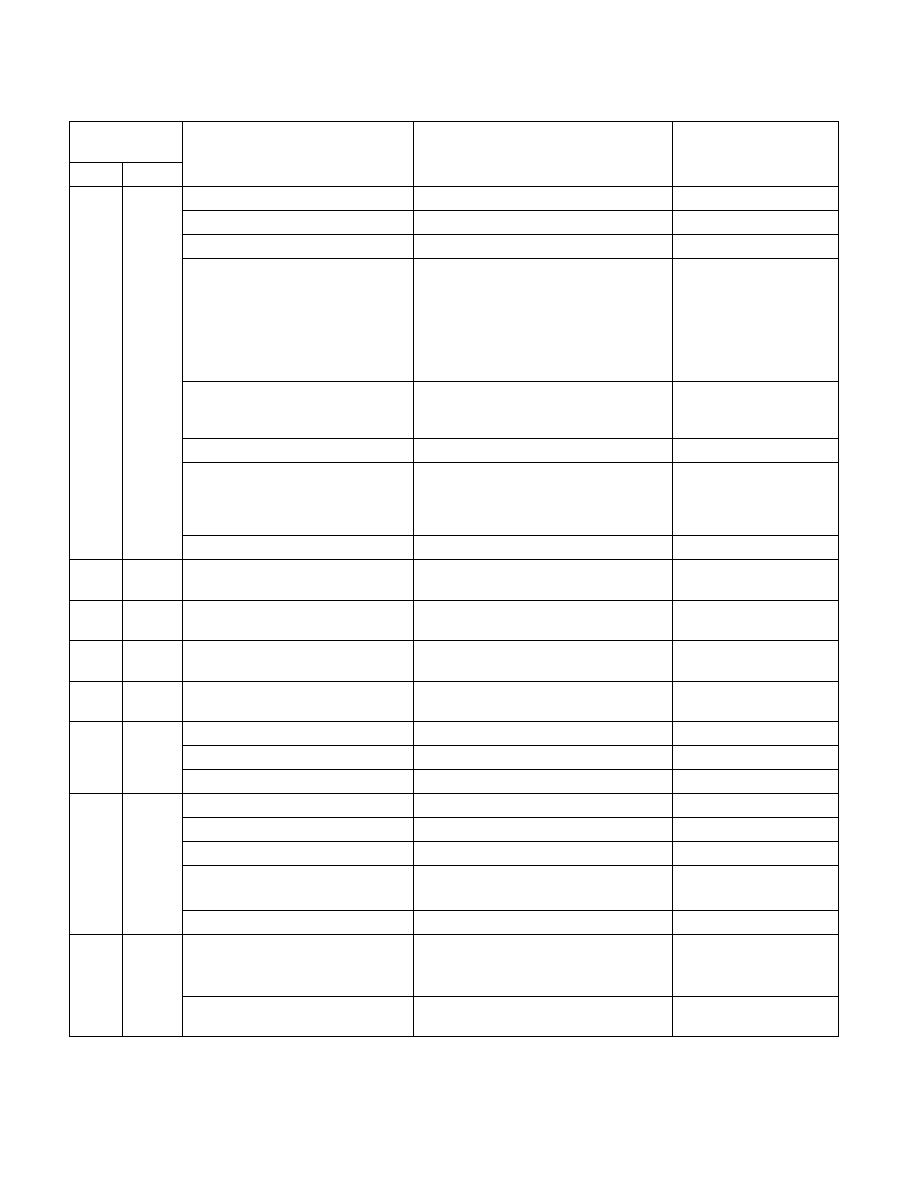

Vol. 3C 35-9

MODEL-SPECIFIC REGISTERS (MSRS)

18

Edge: Enables edge detection if set.

19

PC: enables pin control.

20

INT: enables interrupt on counter overflow.

21

AnyThread: When set to 1, it enables

counting the associated event conditions

occurring across all logical processors

sharing a processor core. When set to 0, the

counter only increments the associated

event conditions occurring in the logical

processor which programmed the MSR.

22

EN: enables the corresponding performance

counter to commence counting when this

bit is set.

23

INV: invert the CMASK.

31:24

CMASK: When CMASK is not zero, the

corresponding performance counter

increments each cycle if the event count is

greater than or equal to the CMASK.

63:32

Reserved.

187H

391

IA32_PERFEVTSEL1 (PERFEVTSEL1)

Performance Event Select Register 1 (R/W) If CPUID.0AH: EAX[15:8] >

1

188H

392

IA32_PERFEVTSEL2

Performance Event Select Register 2 (R/W) If CPUID.0AH: EAX[15:8] >

2

189H

393

IA32_PERFEVTSEL3

Performance Event Select Register 3 (R/W) If CPUID.0AH: EAX[15:8] >

3

18AH-

197H

394-

407

Reserved

06_0EH

2

198H

408

IA32_PERF_STATUS

(RO)

0F_03H

15:0

Current performance State Value

63:16

Reserved.

199H

409

IA32_PERF_CTL

(R/W)

0F_03H

15:0

Target performance State Value

31:16

Reserved.

32

IDA Engage. (R/W)

When set to 1: disengages IDA

06_0FH (Mobile only)

63:33

Reserved.

19AH

410

IA32_CLOCK_MODULATION

Clock Modulation Control (R/W)

See Section 14.7.3, “Software Controlled

If CPUID.01H:EDX[22] = 1

0

Extended On-Demand Clock Modulation

Duty Cycle:

If CPUID.06H:EAX[5] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal