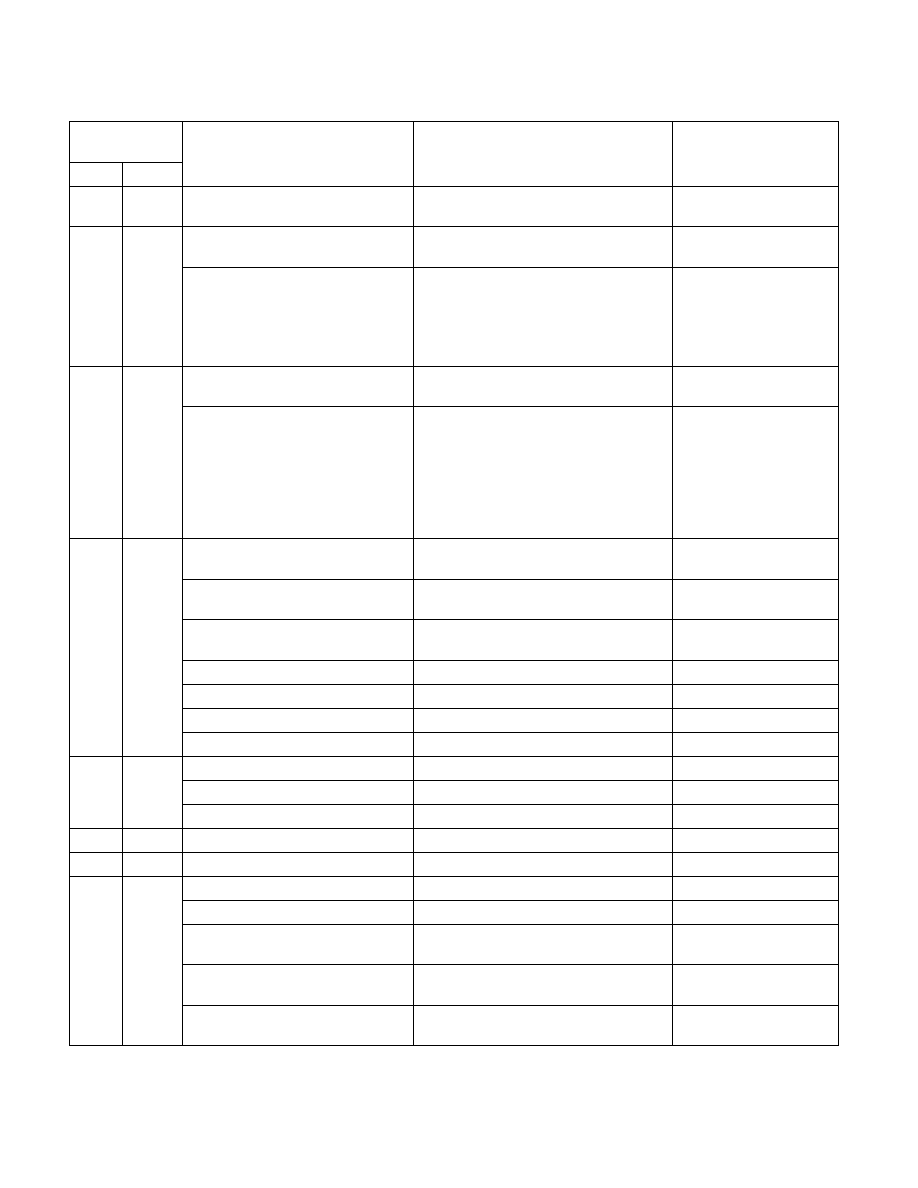

Vol. 3C 35-7

MODEL-SPECIFIC REGISTERS (MSRS)

C8H

200

IA32_PMC7

General Performance Counter 7 (R/W)

If CPUID.0AH: EAX[15:8] >

7

E7H

231

IA32_MPERF

TSC Frequency Clock Counter (R/Write to

clear)

If CPUID.06H: ECX[0] = 1

63:0

C0_MCNT: C0 TSC Frequency Clock Count

Increments at fixed interval (relative to TSC

freq.) when the logical processor is in C0.

Cleared upon overflow / wrap-around of

IA32_APERF.

E8H

232

IA32_APERF

Actual Performance Clock Counter (R/Write

to clear).

If CPUID.06H: ECX[0] = 1

63:0

C0_ACNT: C0 Actual Frequency Clock

Count

Accumulates core clock counts at the

coordinated clock frequency, when the

logical processor is in C0.

Cleared upon overflow / wrap-around of

IA32_MPERF.

FEH

254

IA32_MTRRCAP (MTRRcap)

MTRR Capability (RO) Section 11.11.2.1,

06_01H

7:0

VCNT: The number of variable memory

type ranges in the processor.

8

Fixed range MTRRs are supported when

set.

9

Reserved.

10

WC Supported when set.

11

SMRR Supported when set.

63:12

Reserved.

174H

372

IA32_SYSENTER_CS

SYSENTER_CS_MSR (R/W)

06_01H

15:0

CS Selector

63:16

Reserved.

175H

373

IA32_SYSENTER_ESP

SYSENTER_ESP_MSR (R/W)

06_01H

176H

374

IA32_SYSENTER_EIP

SYSENTER_EIP_MSR (R/W)

06_01H

179H

377

IA32_MCG_CAP (MCG_CAP)

Global Machine Check Capability (RO)

06_01H

7:0

Count: Number of reporting banks.

8

MCG_CTL_P: IA32_MCG_CTL is present if

this bit is set

9

MCG_EXT_P: Extended machine check

state registers are present if this bit is set

10

MCP_CMCI_P: Support for corrected MC

error event is present.

06_01H

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal